# Contents

| 3   |

|-----|

| 4   |

| 6   |

| 17  |

| 29  |

| 37  |

| 47  |

| 59  |

| 69  |

| 75  |

| 89  |

| 111 |

|     |

# Introduction

This is the book I wish I'd had seventeen years ago when I tackled my first verilog design. The idea for this reference is to have you looking at workable examples by the shortest path possible. Like any descriptive language, whether verilog, VHDL, or C++, there are layers of features and capabilities that will ultimately be brought to bear if you use it long enough, but most of which can represent just a confusing distraction if introduced early on. This book initially strips away all but the very bare essentials to show you those fundamental aspects of the language that are universally required in almost any design. Later, it builds, feature-by-feature, more sophisticated capabilities.

The material is intended for students and engineers, both hardware and software, who already have a working knowledge of digital design and operation. It is not an instructional text on how to design logic. Additionally, it is intended to provide a very quick entry into verilog basics; it is not a comprehensive verilog reference. But I'm sure you didn't expect that for less than \$20.

The contexts of the examples assume FPGAs (versus ASICs or, God forbid, discrete logic). This is by far the most ubiquitous use of HDL (Hardware Description Language) today. And in any case, if you're just learning HDL, it is highly unlikely that you've been hired to do ASIC development.

All examples used in this book are available as text files at:

http://www.readler.com

A note about punctuation: commas and periods are generally placed before closing parenthesis. For example, the following words might describe my approach to writing this book: "fastidious," "thorough," and "clarity." However, I have taken the liberty to break this rule throughout the following text in order to avoid confusion about the exact spelling of signal names. So, for example, in this context I might write that "in\_1", "out\_1", and "enable\_b" comprise all the signals of block "mux\_2".

# The Tool Flow

This subject could be a whole book onto itself, but we will limit it here to just what's needed to see how verilog code is used. Verilog, like VHDL, is a hardware description language (HDL), and as such, completely describes how the logic design works. Along with a device-specific file defining implementation details such as device package type, I/O pin assignments, etc., the verilog code is all that's needed to create an operating FPGA. The "operating FPGA" is embodied in a binary object file that is loaded into the device after power-up. The tools described here are used to get from the verilog source code to this loadable binary object file.

#### Step 1: coding

This is simply the process of laying the ideas in your head down into verilog code, which is just a text file. If you've done software coding, you are completely familiar with this step. Any text editor will work, but professional text editors will help by color-coding syntax categories of verilog (assuming your version supports verilog);

#### Step 2: simulation

Although not strictly necessary to achieve a successfully compiled load file, simulation should be considered a practical requirement. Foregoing this step would be like spending months designing, building, and packing a parachute, and then jumping out of a plane without ever testing it. There is a finite possibility your design will work as intended—decreasing rapidly with complexity but more than likely you will see the ground rushing up at you as you engage power and your FPGA does absolutely nothing.

#### Step 3: synthesis

The first two steps were your creative contribution. Step 3 begins the automated process of translating your text into operating logic. The synthesis step can be thought of as a bridge between your human text description and a gate-level representation. Gate-

level here doesn't necessarily mean just AND and OR gates, but includes basic functional blocks as muxes and flip-flops. It is at this step that we find out if our code can be practically translated into logic that can be implemented in an FPGA. The output from the synthesis step looks very much like a netlist. Expensive stand-alone synthesis tools are often used for large or complex designs, but most FPGA vendor software includes synthesis that is quite adequate for many applications.

#### Step 4: compile

Whereas the synthesis of step 3 still comprises somewhat abstract logic constructs, the final compile step maps the synthesis netlist-like logic description into the specific logic and routing resources of the FPGA device. This step is always performed by the vendor software. We can define pins assignments, or let the tool automatically assign them (almost never done on all but the most difficult designs). It is in this compile step that we find out if the design that was synthesizable can actually be implemented into our chosen device. The output of the compile step is the binary load file that is used to configure the FPGA.

## In and Out

First a word about coding style is necessary. What you find in this book are the author's methods developed over many years of practice. The goal should always be to produce readable code that is easy to understand. Different people have different preferences, though, and you will find as many individual styles as there are people coding. About the only absolutely wrong style is no style, i.e., where all the text is smashed to the left margin with no indenting or consistent parenthetical blocking. You should note that there are many shortcuts that could be taken with the code used throughout this book, but you'll never be wrong by including optional parenthesis or block flags, but you could very well cause your code to synthesize in an unintended manner if you make careless eliminations.

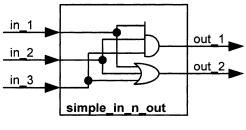

The synthesis tool expects certain standard file structures. We'll start with almost the simplest design possible in order to introduce the minimum requirements: two combinatorial operations on three inputs. Here's how it looks as logic block flow. Note that this box represents the entire FPGA.

Simple In and Out

The verilog code can be seen on the next page. The text file implements one "module," which for this simple design is the entire design. The word "module" is a required keyword, and is followed by the name of the module. For our purposes, a module is always synonymous with a file, so the module name is the same as the file name. Note, though, that the module name has no file extension (which for verilog is always "v", e.g., "simple\_in\_n\_out.v").

endmodule

#### Simple In and Out

A port list follows the name of the module, and defines all the signals in and out of the module, separated by commas. I/O declarations then follow, defining the direction of each signal listed in the port list (as we'll see later, new verilog versions allow the direction declarations to reside directly in the port list).

Following the declarations, the design proper begins. In this simplest case, the design consists of simple combinatorial

assignments. Note that "assign" is a keyword, and indicates a combinatorial operation (also called a continuous assignment). An AND operation is indicated with "&," while "|" indicates an OR. The keyword "endmodule" marks the end of the verilog module (and also the text file here).

The synthesis software ignores everything after a comment flag-two forward slashes-to the end of the line.

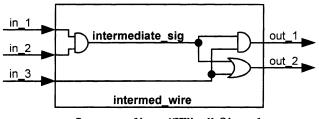

The simple In and Out design just described defines outputs that are direct logical operations of inputs only. Virtually all practical designs, though, will have internal signals. We now introduce the simplest of these, the "wire," which is hardly nothing more than an intermediate stage of combinatorial processing. It is not misleading to think of it as an actual wire connecting internal gates. Note that a "wire" in verilog is technically a type of "net" entity, but in digital design it is common to refer to "wires," along with I/O and outputs of registers, collectively as simply all signals.

In the following example, note that the wire signal—here called "intermediate\_sig"—must be declared as such before it is used. Although verilog allows signal declarations to be done anywhere in the design (before their use), it is standard practice to group them all at the beginning, usually just after the port I/O declarations.

Note that verilog is case sensitive. Some designers use this for effect, delineating similar signals by using the same name but different cases (e.g., the first letter, or the whole name). This is a very good technique if you want to confuse somebody trying to understand your code. If your goal is the opposite, I suggest avoiding this, and using a consistent case throughout.

Intermediate "Wire" Signal

```

11

// Header information

// Intermediate Wire Signals

11

module intermed wire

(

// Inputs

in 1,

in 2,

in 3,

// Outputs

out 1,

out 2

);

// Port definitions

input

in 1;

in 2;

input

input

in 3;

declarations

output

out 1;

output

out 2;

wire

intermediate sig;

// ----- Design implementation ------

assign intermediate_sig = in_1 & in_2;

assign out 1 = (intermediate sig) & in 3;

assign out_2 = (intermediate_sig) | in_3;

endmodule

```

#### Intermediate "Wire" Signal

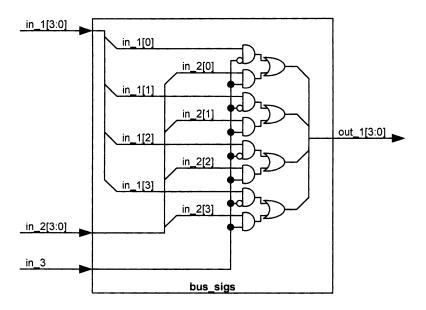

Logic designs often (usually) include multi-bit buses. These are represented in verilog as vector signals, and the width is defined in the declaration (single-bit signals are called scalars). The following example performs a combinatorial operation on two 4-bit input buses (AKA vectors) and a single-bit (AKA scalar) control signal.

#### **Bus Signals**

Essentially, when "in\_3" is low, then "in\_1" is selected, and when "in\_3" is high, "in\_2" is selected. This is of course a two-input bus multiplexer.

Comparing the block flow diagram with the code on the following page, we can see that verilog vector representation of buses provides for compact representation (the logic for a whole bus is contained in one line). We also see, however, a mysterious intermediate "in\_3\_bus" signal. This is due to the manner of logical operation of the "&" and "|" operators (AND and OR). These perform bitwise operations, and expect the two values to be of equal bus size. Thus, the first assign statement extends the single-bit "in\_3" to a 4-bit "in\_3\_bus", whereby all the bits of the

new bus have the same value as the original "in\_3". This is done using a replication operator, where the value of the signal inside the inner pair of braces is repeated the number of times as indicated by the number between the pairs of braces.

Note that "~" is a bitwise negation operator, i.e., it inverts each bit of the vector signal (bus "in\_3\_bus").

```

11

// Header information

// Bus Signals

11

module bus_sigs

(

// Inputs

in 1,

in 2,

in 3,

// Outputs

out 1

);

// Port definitions

input [3:0]

in 1;

input [3:0]

in 2;

in 3;

input

This is replicated this many times.

output [3:0]

out 1;

wire

[3:0]

in_3_bus;

// ------ Design implementation ------

assign in 3 bus = \{4\{in'3\}\};

assign out 1 = (~in 3 bus & in 1) | (in 3 bus & in 2);

endmodule

```

**Bus Signals**

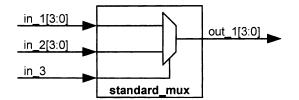

The next block logic diagram shows the logic gates of the previous diagram collected together into a standard mux symbol. Note that we have not changed the function, just the representation.

#### Standard Mux

The verilog code on the opposite page, although also functionally equivalent to the previous code, now reflects a different and more compact way of representing the multiplexer function. We here introduce verilog's combinatorial conditional construct, eliminating the "in\_3\_bus" intermediate signal of the previous example in the process. The assign statement reads as such: "when in\_3\_bus (the select control) is high, select in\_2, else select in\_1." This works very much like a limited version of the familiar IF/THEN statement of other languages.

Note that although a single instance of this conditional selection statement is used here, these can be concatenated. Here's an example:

```

assign final_value = select_1 ? input_1 :

select_2 ? input_2 :

select_3 ? input_3 :

default_val;

```

Here, if "select\_1" is high, "input\_1" is selected, else if "select\_2" is high, "input\_2" is selected, else if "select\_3" is high, "input\_3" is selected, else "default\_val" is selected. Note that a final default value must be included, otherwise the synthesis software will implement a (presumably unintended) latch.

```

assign out 1 = in 3? in 2: in 1;

```

in 1;

in 2;

in 3;

// Port definitions

output [3:0] out 1;

input [3:0]

input [3:0]

input

endmodule

#### Standard Mux

// ----- Design implementation ------

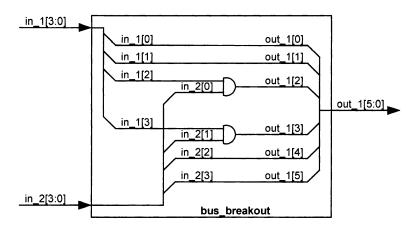

Finally, before we move beyond strictly combinatorial operation, we'll explore a few more details associated with buses. Where in the previous examples we selected entire buses for the output, here we break the buses out and then recombine them after some processing. Note that both input buses are four bits, but the output bus is six bits.

#### **Bus Breakout**

All of the combinatorial and bus reconstruction shown in the module above is implemented in one assignment in the code on the opposite page. Here we introduce bus concatenation, which is defined by a single set of braces. I have arranged the concatenation elements vertically on separate lines for clarity, but they could all be included on the same (albeit somewhat long) line, still separated by commas. Note that the MS element is always first (i.e., next to the left-most brace), while the LS element is always last (next to the right-most brace. Notice also that the first and last elements here comprise two bits, and that the two middle elements (each one bit) are the result of combinatorial operations.

```

module bus_breakout

(

// Inputs

in 1,

in 2,

// Outputs

out 1

);

// Port definitions

input [3:0] in 1;

input [3:0] in 2;

output [5:0] out 1;

// ----- Design implementation ------

assign out 1 = \{ in 2[3:2], \}

(in_1[3] & in 2[1]),

≻concatenation

(in 1[2] & in 2[0]),

in 1[1:0]

};

```

endmodule

**Bus Breakout**

# Clocks and Registers

In the introduction, I indicated that this book assumes that you have a working familiarity with digital design. The rubber is about to meet the road.

Clocked state logic comprises the vast majority of the workings of modern FPGAs, and it is here that the true complexity and sophistication of any hardware descriptive language unfolds. The fundamental principles of clocked operation in verilog, though, are straightforward, and easy to grasp if we take them a step at a time.

Until now, our code has consisted of continuous assignments, i.e., direct combinatorial logic. These "assign" statements are continuous in the sense that the output signal (the one being assigned) is continuously responsive to any and all inputs. Any input that changes (and is not gated off by the intervening logic) will immediately affect the output (ignoring physical delays). Contrary to this, registers hold or store information, and therefore require a different coding mechanism called a structured procedural The most common structured procedural statement, statement. and the one used almost exclusively for register implementations, is the "always block." There are a variety of flavors of this, but for implementation (i.e., synthesis) of clocked registers, we use exclusively the sequential, non-blocking version. That probably doesn't mean much to you, and that's okay for now. It is helpful to know that there are other forms in case you may happen across them, but for the time being, an always-block is synonymous with a register.

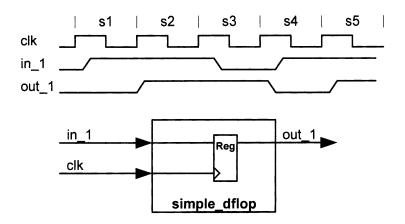

We'll begin by implementing the simplest form of a D-flop. Since this represents the basis for the various forms of registers we will continue to encounter, it is labeled as a "Reg." As shown in the timing diagram, output "out\_1" follows "input in\_1" at the clocked edges.

Simple D-flop

For the sake of brevity we've modified the file format a bit in the code on the opposite page (you'll get used to this as you look across different people's code).

We've added a new declaration for a "reg." This is necessary since we will be implementing output signal "out\_1" as a register type. This is in contrast to the "wire" declaration. We have not previously needed to declare outputs explicitly as wires since in verilog outputs default to wire types (it wouldn't have been wrong to declare all the previous outputs as wires, just not necessary).

The section of code shown as the always-block implements the D-flop register. The information inside the parenthesis next to the "@" symbol is called the sensitivity list, and defines which signals can contribute to changes inside the block. Specifically, no activity inside the block can occur unless something in the sensitivity list changes. In the case of our simplest of D-flop registers, the sensitivity list contains just the clock signal. Further, "posedge" defines the flop as rising-edge triggered ("negedge" would be falling-edge triggered).

The operation is easy to see: at every rising clock edge (and only at a rising clock edge), the value of "in\_1" is assigned to "out\_1". You may wonder why we use the two-part "<=" symbol instead of a simple "=" for the assignment like we did with the combinatorial assignments, and the answer is that this defines it as a

non-blocking assignment. This allows individual elements of more complex always-block structures to operate independently, but the important point is that all synthesized registers use this nonblocking assignment, so get used to it.

The "begin" and "end" lines define the body of the alwaysblock. In this case where there is only one assignment line, the begin/end pair is actually optional, but I recommend always using them for consistency.

```

// Simple D-flop

module simple_dflop ( clk,

in 1,

out 1

);

input

clk;

input

in 1;

out 1;

output

req

out 1;

// ------ Design implementation ------

always @( posedge clk )

always block

begin

out 1 <= in 1;</pre>

end

endmodule

```

#### Simple D-flop

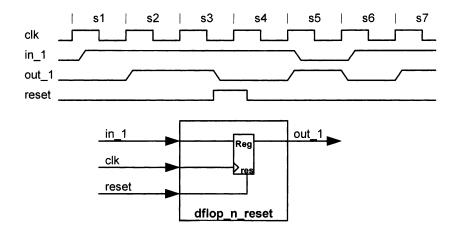

Next we add an asynchronous reset to our simple D-flop. The timing diagram shows the operation where "reset" forces "out\_1" low immediately during state s3, and "out\_1" then remains low until clocked again back high at state s5.

Our convention will be that asynchronous controls (resets and presets) will enter the register box at the top or bottom, while all synchronous controls will connect to the front.

**D**-flop with reset

In the code on the opposite page you can see that the alwaysblock has now grown to accommodate the reset. Since the reset is asynchronous and results in activity immediately, it must be included in the sensitivity list. Tagging it as "posedge" means that it will be high-active—the flop resets as soon as the reset goes high, but after the reset is lifted, the flop doesn't change until the next clock edge, thus only the rising edge of the reset requires immediate attention.

The body of the always-block has now become more complicated as we introduce if/else conditional statements to accommodate the reset. Any time "reset" his high, "out\_1" is forced to zero. Since this happens as soon as reset goes active (reset is part of the sensitivity list), and at every rising clock edge, you can see that this effects an asynchronous clear. When reset is not high, then the "else" original in-to-out register assignment is selected (occurring only at rising clock edges).

Note that the reset zero assignment is made with "1'b0". Verilog uses a specific format for static values. The first field defines the number of bits (i.e., the width of the vector), the next field, separated by the apostrophe, defines the radix, and the last field defines the actual value. Since in this case we have a simple one-bit zero, the first field is "1", and we let the value be defined as binary.

module dflop n reset ( clk, reset, in 1, out 1 ); input clk; input reset; in 1; input output out 1; out 1; rea // ----- Design implementation -----always @( posedge clk or posedge reset ) begin if ( reset ) out 1 <= 1'b0; else out 1 <= in 1; end endmodule

**D**-flop with reset

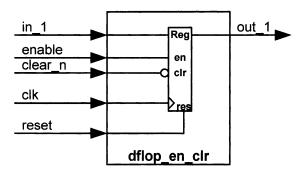

Pressing on, we now add more functionality to our nascent register. Here we introduce two synchronous controls: an enable, and a low-active synchronous clear. We forgo a timing diagram since the operation is self-evident.

Note that the asynchronous reset remains. Besides benefiting from simple consistency, this demonstrates an important point about FPGA design in general: we invariably choose one reset method (synchronous or asynchronous), which is then used globally on all the registers. At a minimum, global resets are necessary for simulation, but additionally may be a practical necessity for proper testing in-circuit. In our case, we will always be using a global asynchronous reset. We should also note that on very large and/or fast designs, the global reset may be segmented into functional domains, but the premise that every flop shares a (semi)common reset remains.

D-flop with enable and clear

The always-block in the code on the opposite page expands with the additional synchronous control functions. The asynchronous reset still takes priority (it comes first), but now a low "clear" signal will also force the output to zero as well. However, since this clear signal is not included in the sensitivity list, the change occurs at the next rising clock edge (thus, rendering it synchronous).

Notice that the "else if" conditional expression uses a logical equality test, whereas the "if" reset line did not. This is because the conditional expression is evaluated as either Boolean true or false. When "reset" is a one, its Boolean equivalent is by definition true. The conditional expression can be as complicated as you like, spanning many lines of code, as long as the synthesis tool is able to determine a final Boolean result.

The final conditional statement implements the clock enable, and here again, since "enable" is high-active, no logic equality test is necessary. Notice that there is no final "else" statement. If there were, the latching operation of the clock enable would be defeated.

As with most other languages, the order of the conditional statements determines the priority.

####

```

module dflop_en_clr ( clk,

reset,

in 1,

enable,

clear,

out 1

);

input

clk;

input

reset;

input

in 1;

input

enable;

clear;

input

output

out 1;

reg

out 1;

// ----- Design implementation ------

always @( posedge clk or posedge reset )

begin

if ( reset )

out 1 <= 1'b0;

else if ( clear == 1'b0 )

out 1 <= 1'b0;

else if ( enable )

out 1 <= in 1;</pre>

end

```

endmodule

#### D-flop with enable and clear

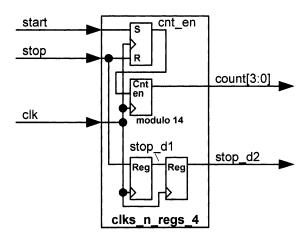

We now introduce a few common state-type operations to show how increasingly sophisticated register-based functions are implemented in always-blocks. A four-bit counter is enabled by a "start" event, and stopped by a "stop" event. The SR flop allows the start and stop events to be short, e.g. one-clock pulses, rather than a continuously enabling flag. Additionally, for further illustration, we delay the start signal two clocks and send it out.

You'll notice that we have not shown the asynchronous reset. This is done for clarity; from this point forward it is assumed. It is implemented in the code, and always will be (in this book).

SR flop and counter

The code includes two register declarations for internal signals (cnt\_en and stop\_d1), and two register declarations for the two external signals (count[3:0] and stop\_d2). We now have multiple always-blocks. Note that always-blocks operate concurrently, meaning they run simultaneously, independent of each other, just like two registers in a design.

Each always-block is associated with a coherent register function: one for the SR flop, one for the counter, and one for the two delays. The SR flop always-block needs no explanation beyond noting that there is no "else" statement, resulting in a latch function (which is indeed what we desire). The counter always-block also has no "else" statement, but since it is an enabled counter, it is also in a sense a latch. Notice that since the counter is modulo 14, the first "else if" statement clears it when the count is 13. A couple of things to note here: "4'd13" indicates a decimal thirteen, and we're now using a double "&&" in the conditional expression. This is because "&&" is a Boolean AND (versus the bitwise "&"), which is required for the conditional decision. In the same sense, "||" is a Boolean OR (versus the bitwise "|"). Note that we use "4'h0" for clearing the counter. This indicates a hex zero. It could just as well have been 4'b0000, or 4'd0. Similarly, the 4'd13 modulo rollover could have been the slightly less readable 4'hD, or even 4'b1101.

start,

```

stop,

count

);

input

clk;

input

reset;

input

start;

input

stop;

output [3:0]

count;

cnt en;

reg

reg [3:0] count;

stop d1;

rea

stop d2;

reg

// ----- Design implementation -----

// SR flop

always @( posedge clk or posedge reset )

begin

if ( reset )

cnt en <= 1'b0;

else if ( start )

cnt en <= 1'b1;

```

else if ( stop )

cnt en <= 1'b0;</pre>

end

```

// Counter

always @( posedge clk or posedge reset )

begin

if ( reset )

count <= 4'h0;

else if ( cnt en

&& count == 4'd13

١

count <= 4'h0;

else if ( cnt en )

count <= count + 1;

end

// delay

always @( posedge clk or posedge reset )

begin

if ( reset )

begin

stop d1 <= 1'b0;

stop d2 <= 1'b0;

end

else

begin

stop d1 <= stop;</pre>

stop d2 <= stop d1;</pre>

end

end

endmodule

```

#### SR flop and counter

The last always-block implements the two sequential delays. The points to note here are that multiple register signals can be grouped into the same always-block (when it makes sense), and that additional begin/end block boundaries are needed around each pair of signal assignments. Without these, the synthesis software might interpret, for example, that "stop\_d2 <= stop\_1" is not associated with the "else," but stands alone.

Finally, we should note that the three always-blocks could be collected together into one. This is shown on the next page.

#### **Clocks and Registers**

```

always @ ( posedge clk or posedge reset )

begin

if ( reset )

begin

cnt_en <= 1'b0;</pre>

count <= 4'h0;

stop d1 <= 1'b0;

stop d2 <= 1'b0;

end

else

begin

if ( start )

cnt en <= 1'b1;

else if ( stop )

cnt_en <= 1'b0;

if ( cnt en

&& count == 4'd13

)

count <= 4'h0;

else if ( cnt en )

count <= count + 1;

stop d1 <= stop;</pre>

stop_d2 <= stop_d1;</pre>

end

end

```

#### SR flop and counter, one always-block

This of course results in more compact code, but the benefit comes with a danger. Extreme care must be taken to make sure there is no ambiguity about what goes with what. If there's any doubt, begin/end block groupings are always available for clarifications.

# State Machines

Everybody loves state machines, particularly people trying to understand your design. But the clarity is only as effective as how well the coding language communicates the state machine's structure. As we'll see, if coded with proper care to outline the operation, verilog provides a very good vehicle.

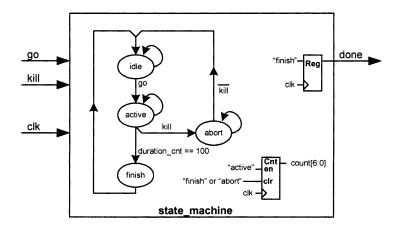

We'll use a fairly simple machine to demonstrate how they can be coded in verilog. After receiving a "go" event, the state machine transitions from the "idle" state to "active," where it waits while an auxiliary counter steps through a hundred clocks. Once this defined active duration is complete, the state machine returns to "idle," but passes through one last "finish" state on the way. This "finish" state produces a one-clock pulse on the "done" output signal. An external "kill" signal can terminate the wait active duration, forcing the state machine back to idle. For the sake of stability, though, the state machine waits in an "abort" state until the kill signal goes back inactive.

Note that this design assumes that the inputs are synchronized to the clock that drives the FPGA. Otherwise, the inputs would need to be clocked through an input register (i.e., synchronized) before presentation to the state machine to prevent spurious operation. In fact, if the extra state latency is not an issue, inputs are often re-clocked as standard procedure.

The "done" register is included to avoid combinatorial decode glitches. Gray or one-hot state coding could be used instead, but including an output register provides a more universal application.

You may recognize that the entire operation of this sample design could be implemented with just the counter alone (enabling and clearing it directly with the external signals), but the state machine presents a clear communication of the intent of the circuit, and also provides an easy avenue for later changes or expansion.

#### State Machine

```

module state machine 1 ( clk,

reset,

go,

kill,

done

);

input

clk;

input

reset;

input

qo;

input

kill;

output

done;

reg [6:0]

count;

reg

done;

reg [1:0]

state reg;

// state machine parameters

= 2'b00;

idle

parameter

= 2'b01;

parameter

active

parameter

finish = 2'b10;

parameter

abort

= 2'b11;

```

#### **State Machines**

```

// ----- Design implementation -----

// State Machine

always @( posedge clk or posedge reset )

begin

if ( reset )

state reg <= idle;</pre>

else

case ( state reg )

idle :

if ( go )

state reg <= active;</pre>

active :

if ( kill )

state reg <= abort;</pre>

else if

(count == 7'd100) state_reg <= finish;</pre>

finish :

state reg <= idle;</pre>

abort :

if ( !kill )

state reg <= idle;</pre>

default :

state reg <= idle;</pre>

endcase

end

// Counter

always @( posedge clk or posedge reset )

begin

if ( reset )

count <= 7'h00;

else if ( state reg == finish

|| state reg == abort

)

count <= 7'h00;

else if ( state reg == active )

count <= count + 1;

end

// done register

always @( posedge clk or posedge reset )

begin

if ( reset )

done <= 1'b0;

else if ( state reg == finish )

done <= 1'b1;

else

done <= 1'b0;

end

endmodule

```

#### State Machine

State machines have limited effectiveness if we are not able to use human-friendly labels, and verilog provides two mechanisms for this. We will be using parameters to bridge alphanumeric state labels with numeric-coded states. As we'll see later, parameters are also often used in verilog designs to carry configuration information down into hierarchical sub-modules, but the advantage they offer for state machine labeling is the fact that they operate locally, i.e., unless specifically communicated into the module, the parameter's value is not affected by other parameter assignments in other modules. So, in general, the same parameter name can be used in different modules, and they will operate independently of each other.

This is not the case for the other possible mechanism for state machine labels: define statements. Unlike parameters, defines are global, meaning that a define assignment in another module could override one in yours. This, of course, could be disastrous if the override is done unintentionally just because the same name happened to be chosen for two unrelated defines.

In the code above, you can see that using parameter assignments we've associated the four states of our design with four distinct numerical (binary) values. We use two bits because that is all we need to define our four states. It would not be wrong to choose a wider bit field, and would provide the modest advantage that the machine would be easier to expand later. An important point is that the parameter assignments are for convenience of labeling only; the actual machine is implemented using a register vector—the two-bit "state\_reg" in our case.

The first always-block implements the state machine using a case statement. Case statements are familiar if you have experience with almost any type of programming, but in a nutshell, the case statement selects and executes the statement group (identified with a following colon) that matches the value inside the parenthesis ("state\_reg" in this example). Since the case statement is contained inside a clocked always-block, an assessment and one selected group is executed each clock.

We'll follow through some of the operation for demonstration. We start with the state machine in the idle state, where "state\_reg" contains "idle" (2'b00). Each clock, the case selection executes the idle group, where if "go" is not high (not active) then nothing is done, so that for the next clock "state\_reg" still contains "idle." Eventually "go" transitions high, and "state\_reg" is assigned "active". This corresponds to the first transition of the state machine. For the next clock, the case statement selects for execution the "active" group, where "state\_reg" remains unchanged until either "kill" goes high, or the counter reaches its terminal value (decimal 100), when the state machine then transitions to "abort" or "finish" respectively.

We'll not detail the entire machine operation, as you've surely gotten the gist by now. Note, however, that "!" is used to indicate "not kill." This is the same as " kill == 1'b0". Like the double "&&" and "||", "!" is a logical operator, and is normally used in conditional expressions. The "~" symbol (a bitwise negation) is usually used in combinatorial assignments. Since the results are often the same, designers sometimes use them indiscriminately.

We'll now review the coding structure. Normally the assignment statement (e.g. "state\_reg <= active") follows the conditional statement on the next line. Here, though, we have it following on the same line. Verilog doesn't care, and this allows for a visually coherent form—the state machine operation is easily understood based on the transition decisions. We note that this is only possible because this always-block contains nothing but the state machine. If it didn't (as we'll soon see), then we would have to block multiple assignments with begin/end borders, ruining the regular matrix structure.

Finally, be aware that many synthesis programs require the default statement, even if the case statement already includes all possible selection branch combinations (considered "full"). The label "default" is a keyword (it was not defined as a parameter).

The counter and output register of this module are similar to those we've already looked at. Note that we decode state machine states directly in these blocks using the "state\_reg" register signal and the state parameters. Also note that the "done" output is set to one based on a conditional "else if" test of the state machine. Most newer synthesis tools allow a more direct form:

```

always @( posedge clk or posedge reset )

begin

if ( reset )

done <= 1'b0;

else

done <= ( state_reg == finish );

end</pre>

```

Here the Boolean result of the state register comparison is translated to a binary bit for assignment to "done."

As we've noted, verilog code can be structured in a variety of ways. Some designers might prefer the auxiliary counter and output register to be collected into one always block along with the state machine. This is how it might look:

```

// State Machine

module state machine 2 ( clk,

reset,

qo,

kill,

done

);

input

clk;

reset;

input

input

qo;

kill;

input

output

done;

reg [6:0] count;

done;

reg

reg [1:0] state reg;

// state machine parameters

parameter idle = 2'b00;

parameter active = 2'b01;

parameter finish = 2'b10;

parameter abort = 2'b11;

// ----- Design implementation -----

// State Machine

always @( posedge clk or posedge reset )

begin

if ( reset )

begin

state reg <= idle;</pre>

```

#### State Machines

```

count <= 7'h00;

done <= 1'b0;</pre>

end

else

case ( state reg )

idle :

begin

count <= 7'h00;

done <= 1'b0;</pre>

if (go)

state reg <= active;</pre>

end

active :

begin

count <= count + 1;</pre>

done <= 1'b0;</pre>

if ( kill )

state reg <= abort;</pre>

else if ( count == 7'd100 )

state reg <= finish;</pre>

end

finish :

begin

count <= 7'h00;

done <= 1'b1;</pre>

state reg <= idle;</pre>

end

abort :

begin

count <= 7'h00;

done <= 1'b0;

if ( !kill )

state reg <= idle;</pre>

end

default :

begin

count <= 7'h00;

done <= 1'b0;

state_reg <= idle;</pre>

end

endcase

end

endmodule

```

#### State Machine, one always-block

Besides losing the visual advantage of correlating the state machine decisions with corresponding actions, this type of code structure is susceptible to mis-operation if care isn't taken to account for every register state in every case selection. Although often resulting in code that is not as tight, when each function is implemented with its own always-block, each operation is clear and concise.

# Modular Design

The design examples we've used so far have been very small for obvious reasons. Designs of increasing complexity reach a point where containing them in a single file becomes cumbersome. At some point sheer size compels us to break up the design into component parts, possibly multiple layers of hierarchy.

There are other good reasons besides just size, though, to use a modular approach:

o reuse (components of a design can be used in multiple places without repeating all the code details);

o pre-existing designs (code developed elsewhere can be incorporated as a "black box" without caring about constituent details);

o clarity (the code can be segmented into functional pieces that correspond to blocks described in high level descriptions);

o simulation (individual pieces of the design can be often times be simulated more rigorously and completely than when embedded in the larger operation);

o changes (by compartmentalizing the functioning, the consequences of changes can be studied and simulated in isolation).

Now having effused about the benefits of modular design, we immediately offer caution against overuse. Keep in mind that anyone examining your code will need to navigate through as many files as there are modules. No one will love you if you break out every register, mux, and counter as its own instantiated module, when the associated always-block would have taken no more room than the instantiated module that's replacing it.

With that admonishment out of the way, we can proceed to look at how modules are instantiated within other modules.

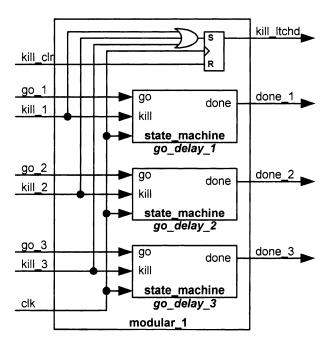

For the first example, we will use the module design from the previous section (State Machines) for our internal instantiated module. Note that there were two coded versions of that, but since they operate exactly the same, and have the same input/outputs, we could use either one.

First Modular Example

Here, we've instantiated three copies of the state\_machine module in a new higher-level module (sometimes called a "wrapper" when most of the code consists of instantiated sub-modules) called "modular\_1". We've labeled the first instantiated copy as "go\_delay\_1", the second as "go\_delay\_2", and the third as "go\_delay\_3". Additionally, we've also added an SR latch to detect if any of the modules' internal counts were "killed," and have provided a signal (kill\_clr) to clear the latch.

On the next page is the code file for "modular\_1".

#### **Modular Designs**

```

module modular 1 (

clk,

reset,

go 1,

kill 1,

go 2,

kill 2,

go 3,

kill 3,

kill clr,

done 1,

done 2,

done_3,

kill ltchd

);

clk;

input

input

reset;

go 1;

input

kill 1;

input

input

qo 2;

kill 2;

input

go 3;

input

kill_3;

input

kill_clr;

input

done_1;

output

done 2;

output

done 3;

output

kill ltchd;

output

req

kill ltchd;

// ----- Design implementation -----

// first module instantiation

state machine 1 go delay 1

(

.reset ( reset

),

.clk

( clk

),

.go

( go 1

),

( kill_1 ),

.kill

.done ( done 1 )

);

// second module instantiation

state machine 1 go delay 2

(

.reset ( reset ),

```

```

.clk (clk ),

.go (go_2),

.kill (kill_2),

.done (done_2)

);

// third module instantiation

state machine 1 go delay 3

(

.reset ( reset

),

.clk (clk),

.go (go_3),

.kill (kill_3),

.done (done_3)

);

// Kill Latch

always @( posedge clk or posedge reset )

begin

if ( reset )

kill ltchd <= 1'b0;

else if ( kill 1

|| kill 2

|| kill 3

)

kill ltchd <= 1'b1;</pre>

else if ( kill clr )

kill ltchd <= 1'b0;

end

```

endmodule

#### First Modular Example

The entire module design consists of three lower-level module instantiations, followed by one always-block for the SR latch. Each module instantiation includes:

o the name of the instantiated module (state\_machine\_1);

o followed by a label (e.g., "go\_delay\_1" or "go\_delay\_2");

o and a port connection list, where the connections are made between the instantiat-<u>ing</u> module and the instantiat-<u>ed</u> module.

A period precedes each port signal of the instantiat-<u>ed</u> module, while the connecting signal of the instantiat-<u>ing</u> module follows inside parenthesis. Note that each connection signal pair is separated by a comma. Keep in mind that the instantiat-<u>ing</u> name of the instantiat-<u>ed</u> module (state\_machine\_1) must match exactly that of the instantiat-<u>ed</u> module (and therefore the actual file name, minus the ".v" extension). It often happens that multiple versions of a file may have the same name, located in different folders. You will explicitly tell the synthesis software where the one you want to use resides.

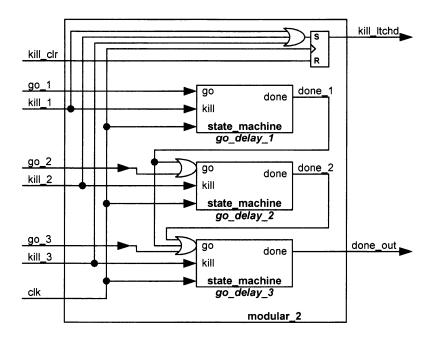

Next, we make a minor change to our example modular design. Each module stage now ORs its "go" input with the previous stage's "done" output.

Second Modular Example

```

// Modular Design #2

module modular 2 (

clk,

reset,

go 1,

kill 1,

go 2,

kill 2,

go 3,

kill 3,

kill clr,

done out,

kill ltchd

);

input

clk;

input

reset;

input

go 1;

kill 1;

input

go 2;

input

kill 2;

input

input

go 3;

kill 3;

input

kill clr;

input

output

done out;

output

kill ltchd;

kill ltchd;

reg

wire

done_1;

wire

done 2;

// ----- Design implementation -----

// first module instantiation

state machine 1 go delay_1

(

.reset ( reset

),

.go (go_1 ),

.kill (kill_1),

.done (done 1

.clk

),

);

// second module instantiation

state_machine_1 go_delay_2

(

.reset ( reset

),

( clk

.clk

),

.go

( done 1 | go_2 ),

```

```

.kill ( kill_2 ),

.done ( done 2 )

);

// third module instantiation

state machine 1 go delay 3

(

.reset ( reset ),

.clk ( clk

),

( done 1

.qo

| done 2

| go 3

),

.kill

( kill 3 ),

.done ( done_out )

);

// Kill Latch

always @( posedge clk or posedge reset )

begin

if ( reset )

kill ltchd <= 1'b0;

else if ( kill 1

|| kill 2

|| kill 3

)

kill ltchd <= 1'b1;

else if ( kill clr )

kill ltchd <= 1'b0;

end

```

endmodule

#### Second Modular Example

Notice that the "done\_1" and "done\_2" outputs of the first example design now become wires. This is necessary since every signal (i.e., net) must be declared. As we learned earlier, the original "done\_1" and "done\_2" outputs were also wires by default. Once we remove the output declarations, though, we must now explicitly declare them as wires.

The second point to notice is that we've performed the interstage ORing right inside the port connection list. Isn't verilog cool?

(As a minor point, you might look at how we've structured the ORing differently for the second and third stages).

Instantiated modules are not limited to your own verilog code, or even to code that was written by another designer of your acquaintance. Instantiating sub-modules is the method we use to incorporate a variety of functionality delivered as tested and documented components. These include "IP cores"-code, sometimes quite substantial and complex, provided (often sold) by third-parties that implement a well-defined set of functions. Common examples of cores are complete micro-processors. You could, if you wanted, include a PowerPC<sup>™</sup> in your design. Other examples of off-the-shelf cores are PCI interfaces, video encoder/decoders, encryption blocks for data security (e.g., DES and AES), and error detection/correction (e.g., Viterbi and Reed-Solomon). There are probably as many IP cores as there are useful segmentable functions. Many are available from the FPGA vendor directly. Some are fixed, straight-forward functional blocks, such as 8b/10b encoder/decoders. Others are synthesized based on designer-provided parameters during the design process by vendorspecific software that comes integrated as part of the FPGA vendor's tool suite, or purchased separately. Examples of these sorts of cores are FFT and FIR filter DSP blocks, Gigabit Ethernet interfaces, and FIFOs.

Another important class of vendor-provided modules is primitive cores. These are functionally simpler blocks that are either built directly into the FPGA device fabric, or are synthesized in a way that utilizes fabric specifics that would not otherwise be visible to general third-party synthesis tools (thus the label primitive). The key difference between primitive cores and the afore-described off-the-shelf IP cores is that, whereas the latter generally consist of verilog code that becomes a part of the overall synthesized design, primitive cores are just place-markers in the code that the vendor compiler (versus the synthesis stage) recognizes and inserts the proper functionality at the device-specific stage of the path towards a final binary build file. These placemarkers are called "black boxes," and have the appearance in the code of a normal instantiated module. However, no associated verilog file exists to go along with them. In fact, most synthesis software upon encountering an instantiated module for which it cannot find an associated verilog file will automatically declare it as

a black box entity. Designers, as a result, must routinely scan synthesis results looking for instances of black box declarations in case they are simply the result of lost or misplaced verilog files.

Primitive cores will be addressed again in the next section on memories.

A final word about module instantiations, and we tread here with trepidation. We have shown you how to make inter-module port connections using a connection list, where each instantiat-<u>ed</u> module's I/O port is paired with an instantiat-<u>ing</u> module's signal. There is no ambiguity in this: each port is specifically identified with its associated signal. However . . . verilog does allow another short-cut method, called an "ordered list." Here, only the instantiat-<u>ing</u> module's signals are listed, and the instantiat-<u>ed</u> module's I/O ports are inferred based on their position. An ordered list module instantiation from the previous code might look like this:

// first module instantiation, using an ordered list

go\_delay\_1 state\_machine\_1

( reset, clk, go\_1, kill\_1 , done\_1 );

Now that we've revealed this, it's like cracking the top of Pandora's Box. You can see the attraction-simple and short; but also prone to mistakes. In fact, I go so far as to consider this method a trap waiting to be sprung. The reason is that port misconnections are not obvious, and if the mismatched port types are the same, then the synthesis tool will not flag a problem. Mismatches can happen if, for example, modifications are made to the instantiat-ed module that cause the ordering of the port list to change (remember that often the instantiat-ed module is not under your control). Worse still, verilog allows you to leave unconnected output ports of instantiat-ed modules out of the port list. This means that if, for example, a new output signal is added to your instantiat-ed module (this happens quite often), shifting down all the original signals, and if the last signal is an output, it is now unconnected (and signals above are misconnected), but no error flag is raised by the tools.

I urge you to resist.

## Memories

Memories are an important component in many fields of digital design, and they come in a variety of forms: DRAM, SDRAM, DDR, QDR, SRAM, FIFO, LIFO, DP, etc.. Of these, the first four are of course not (yet) available for FPGA implementation, but almost any other form imaginable has probably been implemented. Memory design in FPGAs is another topic that could be a whole book unto itself, and here we will simply review the fundamentals of designing memories using verilog.

Memories implemented in FPGAs (versus memory controllers, which would also include the DRAMs, etc.) can be defined in three general ways:

1) infer the memory directly via the verilog code;

2) build the memory using the vendor's primitive RAM structures;

3) design the memory using the FPGA vendor's specialized tools.

We'll discuss the last two first. The second option (primitive RAM structures) uses RAM resources that are built into the FPGA device fabric, and thus are the most efficient means of building memory functions (and if you don't use them, then they represent valuable substrate that goes unused). Each RAM block occupies a fixed amount of FPGA die, and they usually have a limited degree of flexibility as to their depth versus width (aspect ratio). These RAM blocks are an example of primitive cores discussed in the previous section, and as explained there, when using these in a verilog design, they are instantiated as black box modules. In this mode, it's up to you the designer to build up in verilog any associated control logic, such as circular addressing for FIFOs, logic for the FIFO depth flags, etc.. Most built-in FPGA RAM blocks can be configured to operate as dual-port memories, vastly simplifying many designs.

The third option (vendor's specialized tools) is by far the easiest approach, particularly with application-specific FIFOs. This method was also discussed in the previous section, and functional blocks built around memories (FIFOs, ROMs, CAMs, etc.) are just an example of the IP cores built using vendor-specific software. The designer, via the GUIs of the vendor software, establishes the parameters of the memory functional block. Parameters for FIFOs, for example, might include depth, input width, output width, various flag locations, etc..

The main downside to using vendor-supplied IP core generators is that they depend on vendor-supplied software. This limits the design's portability, meaning that, should the design be moved to another vendor's device (e.g., migrate to an ASIC), all those IP cores will need to be re-designed, either using the new vendor's IP generation tool, or built up anew in verilog. Either way, this often translates to a major design and test effort. If, on the other hand, you are confident you will never change FPGA vendors, then this is not an issue.

However, even if you never change FPGA vendors, there still may be issues related to the vendor's IP generation tool evolution. If you knew that you were going to create the design just once and never revisit it again, there would be no problem. But in practice, this almost never happens. Whether from requirement changes introduced later, or subtle problems found down the road that require modifications, inevitably the design sees changes. If the changes manifest in one of the vendor-generated cores, then the IP module will need to be re-generated, and this in turn may require you to use a newer version of the vendor core generation tool. Although rare, there sometimes are differences in how the new tool creates the functions, particularly when the vendor replaces a whole category subset of the tool with a completely "new and improved" Also, again though rare, a vendor may completely version. eliminate support for an esoteric, infrequently used type of core.

Lastly, we go back to the first method of defining memories: inferring the memory directly via the verilog code. This is the method used when the design is expected, or even suspected, to migrate later to an ASIC, where RAM blocks and convenient GUIbased vendor IP generators are but a rumor. Also, inferred memories are often used for very small memories—specifically, memories significantly smaller than the smallest primitive RAM block (we may be saving those for places where they are really needed).

First, we should explain why we say that the memory is "inferred," and not just implemented in the code like a register or mux. Synthesis tools—whether FPGA or ASIC—include specialized capabilities to recognize when a memory is being implied (AKA inferred). The reason is that the tool can then take advantage of those memory resources at its disposal (specific to the chosen device). In the case of FPGAs, this may ensure that the synthesis tool uses RAM blocks if appropriate (and allowed by the user). Even if primitive IP blocks are not used, the synthesis tool may take special precautions (e.g., coordinated timing) when constructing a memory from verilog code, but only if it recognizes it as such.

Each synthesis tool may have its own particular requirements associated with inferred memories, but one aspect that virtually all have in common is that they expect the memory to be implemented as an array of registers. Verilog has a specific declaration and syntax usage for register arrays. Here's an example of a register array declaration:

```

reg [7:0] mem_buf[0:127];

```

This declaration defines an array of 128 8-bit registers. Note that the vector size ([7:0]) is located in the same place as the familiar single-instance register (between "reg" and the register name, "mem\_buf"). The array size declaration then follows the register array name (in this case, [0:127]). You should note that verilog allows virtually any combination of numbers in the array size field. Thus, "[127:0]", "[0:1]", and "[1:10]" are all legal, the last being an array of ten registers. That said, memory implemented via verilog code is almost always declared as an array of either "[0:x]" or "[x:0], where "x" is the memory size minus one. The reason for this is that the logic that generates the write and read addresses is generally zero-based, i.e., for a 16-word memory, the address signals will consist of 4-bit values (0 through 15, i.e. 4'h0 through 4'hF).

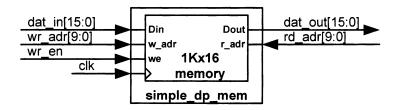

The following is a simple dual-port memory. Data flows in one direction, entering from the left through a write port, and accessed from the right via a separate read port.

Simple Dual-port Memory

We will implement this as a fully synchronous memory, meaning that both the input and output data are clocked (versus, for example, that the output data changes as soon as the read address changes). This does not mean, however, that the write or read addresses are registered (otherwise, the write address would have to come one clock before the associated data to be written). Therefore, write data (dat\_in) is presented to the memory during the same clock as the write address (wr\_adr), but the read data (dat\_out) appears out of the memory one clock after the read address (rd\_adr).

#### Memories

```

output [15:0] dat_out;

input [9:0] rd_adr;

reg [15:0] memory[0:1023];

reg [15:0] dat_out;

// ----- Design implementation -----

// Memory

//

always @( posedge clk )

begin

if (wr_en)

memory[wr_adr] <= dat_in;

dat_out <= memory[rd_adr];

end

endmodule

```

#### Simple Dual-port Memory

So, notably, here we are representing the greatest quantity of FPGA logic so far with the least amount of verilog code. We see now how a register array ("memory") implements a memory; the addresses, both write and read, each point to one location (or word) in the array. If the write enable signal (wr\_en) is active, at the rising edge of the clock the write data word (dat\_in) is loaded into the register array at the location specified by the write address (wr\_adr). Simultaneously, the value located at the location specified by the read address (rd\_adr) is loaded into the memory's output register (dat\_out).

Left to the fate of chance by ambiguity, this code would probably result in the synthesis software using the RAM block resources of the FPGA if available. Explicit direction can be included to direct the synthesis tool to either specifically use RAM blocks or specifically not use RAM blocks (in which case the memory is then referred to as distributed RAM). Each synthesis tool has its own format for these types of embedded directions, and the designer must consult the tool's documentation for guidance. In general, though, the synthesis directions are communicated via comments in the verilog code that include one or more keywords that the tool recognizes (strictly speaking this violates the premise of a comment). Here is an example—this directs the Xilinx XST

synthesis software to implement the memory not as RAM blocks, but as distributed RAM:

//synthesis attribute ram\_style of memory is distributed This comment would be placed just prior to the memory register array declaration. Note that "memory" in the comment is the label of the register array in our code.

Note that although "reset" is brought into the module, it is not used in our memory implementation (in fact, it's not used at all, which is permissible in verilog). This is because RAM blocks, per se, do not have resets. If we wanted to implement the memory as distributed RAM, we would have to consult the vendor's FPGA documentation to see if resets are allowed. We should also note that the ascending/descending direction of the array size field is irrelevant. We declared the array size as "[0:1023]", but we could have equally declared it as "[1023:0]".

Finally, we need to address a troublesome point regarding the memory's operation when a write and read are made to the same address simultaneously. There are two possibilities: 1) the data that is read is the original value before the write replaced it (called "read-before-write"), or 2) the data is the new value that is being written (called "write-before-read"). Our code implies a write-before-read operation based on the simple fact that the write assignment comes before the read assignment in the always-block (reversing the order would imply a read-before-write). Newer RAM blocks typically accommodate either type of operation, but some older versions are fixed, and in that case, as the designer you would have to make sure your code matches (and that your design operates correctly).

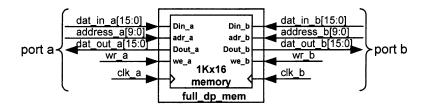

Next, we look at a full dual-port memory, where both ports have both write and read capability.

**Full Dual-port Memory**

As with the simple dual-port memory, this memory is fully synchronous, where write data  $(dat_in_[a/b])$  is presented to the memory during the same clock as the address  $(address_[a/b])$  for writes (when wr\_[a/b] is active), but the read data  $(dat_out_[a/b])$ appears out of the memory one clock after the address for reads (when wr\_[a/b] is inactive). If you're not familiar with full dualport memories, note that data written from either port can be read from either port—the contents of the memory are shared between the two ports. Note that we've also added a second clock, so that each port is now clocked independently (both ports could share a clock if independent clocking is not needed).

```

// Full Dual Port Memory

module full dp mem

( reset,

// port a

clk a

dat in a,

address a,

dat out a,

wr a,

//port b

clk b

dat in b,

address_b,

dat out b,

wr b

);

```

```

input [9:0] address a;

output [15:0] dat out a;

wr a;

input

input

clk b;

input [15:0] dat in b;

input [9:0] address_b;

output [15:0]

dat out b;

wr b;

input

reg [15:0] memory[0:1023];

reg [15:0] dat_out_a;

reg [15:0] dat_out_b;

// ----- Design implementation -----

// Port a

11

always @( posedge clk a )

begin

dat out a <= memory[address a];</pre>

if (wr a)

begin

dat out a <= dat in a;</pre>

memory[address a] <= dat in a;</pre>

end

end

// Port b

11

always @( posedge clk b )

begin

dat out b <= memory[address b];</pre>

if (wr b)

begin

<= dat in b;

dat out b

memory[address b] <= dat in b;</pre>

end

end

endmodule

```

#### Full Dual-port Memory

For as much complexity as a full-featured dual-port memory contains, the verilog code is still relatively simple. Since each port operates from its own dedicated clock, we use separate identical (other than signal names) always-blocks for each. Whereas for the simple DP memory, each port was dedicated as either a write or a read, now each port includes both modes. Since each port shares

#### Memories

an address for reading and writing, the question arises as to what happens to the read output during write cycles. In the case of this code, the operation is essentially write-before-read, meaning that when wr\_[a/b] is active, the data presented on dat\_in\_[a/b] is copied to the read signal dat\_out\_[a/b]. However, whereas for the simple DP memory code the write-before-read was implied, here the operation is explicitly defined with the "dat\_out\_[a/b] <= dat\_in\_[a/b]" assignment inside the write "if" statement. Analyzing the always-block, we see that first the read assignment is made, and if this is not a write cycle (i.e., wr\_[a/b] is not active), then we are done. However, if this is a write cycle, (wr\_[a/b] is active), then the write data (dat\_in\_[a/b]) replaces the value that was read from the memory array on the read output signal (dat\_out\_[a/b]) before the write data is loaded into the specified address location.

But this introduces an important point. For the first time we see a signal being assigned values from within two different statements within an always-block (there were previously multiple assignments—the if-else and case statements—but they were all within the same statement). This is allowed in verilog, and the rule is that the assignment that is ultimately used is the last one executed. Of course, the "last one" may be different for each execution of the always-block (i.e., from clock to clock).

Although supported by the verilog language, assignments from within multiple statements should be used with caution. Even though the results can be predictably simulated, when synthesized into actual hardware, the operation may not always be what you expect. Additionally, the code tends to be more difficult to read with assignments made across multiple statements, especially in large always-blocks.

Speaking of multiple assignments, notice that, not only do we assign the output data from within two statements within the same always-block, but in this code we also make assignments from within two different always-blocks—assigning the memory with write data. This is normally a no-no, and would be as a minimum flagged as a warning by the synthesis software, and possibly as an error. In this case, though, it is appropriate since we are expecting the synthesis software to recognize that the two always-blocks go together to form one structure (the DP memory).

The dual always-blocks bring us to a last subject regarding this full dual-port memory: simultaneous accesses to the same address from the two ports (as implemented in the two always-blocks). This could be two simultaneous writes, or a write and a read. With the previous simple dual-port structure with one clock, we had the means to define what should happen—either write-before-read, or read-before-write. Here, though, because each port operates off its own clock, we have no mechanism in verilog to describe what should happen. In this case it is up to the synthesis software, and possibly the hardware fabric itself.

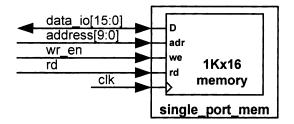

Lastly we look at a simple single-port memory—a type that is almost never used in FPGAs in any substantial way. The reason is that FPGA memory, whether RAM blocks or distributed, is based on d-flop registers rather than bone fide memory cell elements. Thus, RAM blocks inherently provide separate write and read ports; in fact, extra logic must be used to implement a single-port memory over a simple dual-port. We present this structure for illustration only.

Single-port Memory

Data to be written is presented along with the write address and an active "wr\_en" all during the same clock, while for reads, the read address along with an active "read" are presented during one clock, and the data appears one clock later. Since there is only one port, the data bus is bi-directional (input for writes, output for reads).

#### Memories

```

// Single-port Memory

module single port mem

( clk,

reset,

data io,

address,

wr en,

rd

);

input

clk;

input

reset;

inout [15:0] data_io; //new I/O type

input [9:0] address;

input

wr en;

input

rd;

reg [15:0]

memory[0:1023];

reg [15:0]

dat out;

reg

rd d1;

// ----- Design implementation -----

// Memory

11

always @( posedge clk )

begin

if (wr en)

memory[address] <= data io;</pre>

dat out <= memory[address];</pre>

rd dl

<= rd;

end

assign data io = rd d1 ? data out : 16'bz;

endmodule

```

#### Single-port Memory

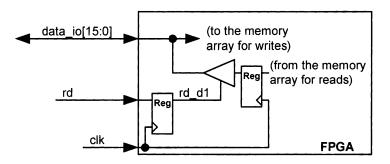

We introduce a new I/O port type; the "data" signal is declared as an "inout." This is verilog's way of defining bi-directional signals. If "wr\_en" is active, data driven onto the bi-directional data bus (data\_io) from some source external to the FPGA is loaded into the "address" memory location. The data at this location is also registered into "data\_out", but this goes into the bit-bucket.

If instead of "wr\_en", "rd" is active, then along with the data in memory being registered as "data\_out", the active "rd" is also registered (i.e., delayed) as "rd\_d1". During the following clock (when "rd\_d1" is now active) the memory data being held in "data\_out" is driven onto the external bi-directional data bus "data\_io" by the assign statement. Thus, for reads, the addressed memory data appears one clock after the read (rd) control is active. You may remember that this is how the dual-port structures worked as well. When reads are not occurring (i.e., when "rd\_d1" is not active) the bus is tri-stated via "16'bz"—meaning "16 bits of highimpedance 'z'".

This assignment statement—using tri-state internal buffers—is the key method to implement bi-directional buses. The following diagram illustrates the tri-state buffer as it would appear in our code.

Tri-state buffer for bi-directional I/O

# Managing Clocks

Synchronous design is synonymous with clocked operation, and virtually all non-trivial FPGA designs use one, and often multiple, clocks. It is difficult to understate the importance of ensuring sound, precise clocking. For large, complex printed circuit board designs, this is often a dedicated development sub-system—a design specialization. Fortunately, the FPGA manufacturers have invested commensurate effort in developing reliable integrated clocking resources. Their engineers have developed a sophisticated clock generation, management, and distribution sub-system for you.

The clocking resources in FPGAs can be grouped into two categories: 1) clock distribution, and 2) clock synthesis. We have now encountered two uses of the word "synthesis," but whereas our first instance pertains to the formal definition of the word, whereby the verilog code synthesis software "combines components to form a connected whole," clock synthesis, as we shall see, is more a process of creating modified versions of something (in this case, from a source clock).

The first category of clocking resource—distribution—consists of specialized FPGA buffers and routing facilities. Clock buffers are essentially current amplifiers powerful enough to drive a clock into the multitude of loads at far-flung locations with enough umph to ensure that the clock edge can arrive at each destination with minimum delay (and all at the same time, i.e., with no skew). In order to achieve this, the routing paths along the way must also be robust enough not to impose a load, meaning that they need to have sufficient metal. To this end, FPGAs have dedicated routing just for clocks.

Accessing these special clock buffers (often called global buffers) and associated robust routing structures can be achieved in verilog code by instantiating the clock buffer directly. Since the robust low-skew routing is driven directly by the buffer, it comes

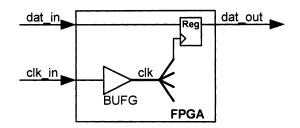

along for free. The following diagram shows a Xilinx clock buffer (BUFG), but each FPGA vendor has its own version. For example, the predominant Altera clock buffer is called "GCLK".

**Clock Buffer**

The following code shows the clock buffer instantiation, which looks like the module instantiations we saw earlier, because, of course, this is exactly what it is. The "BUFG" clock buffer is a vendor primitive, and is interpreted by the synthesis software as a black box (recall that the synthesis software simply passes these down to the vendor compiler, which presumably knows what they are). We recognize that once we begin using vendor-specific primitives, we are dedicating our code to that vendor.

```

// Clock Buffer

module clock buffer

( reset,

clk in,

dat in,

dat out

);

input

reset;

input

clk ;

input

dat in;

output

dat out;

wire

clk;

dat out;

reg

```

```

// ----- Design implementation -----

// clock buffer instantiation

BUFG clock buffer inst

(

.I (clk_in),

.0 ( clk )

);

// register

always @( posedge clk or posedge reset )

begin

if ( reset )

dat out <= 1'b0;</pre>

else

dat out <= dat in;</pre>

end

endmodule

```

#### **Clock Buffer**

This example used an external clock input, but it is usually possible to drive internally sourced clocks though clock buffers as well. One example is when receiving a high-speed serial interface (e.g., Gigabit Ethernet), where the Serdes IP core recovers the line clock, which must then be used for portions of the internal operation.

Sometimes the FPGA will have special dedicated clock inputs that connect to internal clock buffers directly, further reducing delay and skew. For example, most Xilinx FPGAs have dedicated clock inputs that are labeled as "GCLK" (making it a bit confusing when comparing to Altera devices, since they use the label for their clock buffers). Since dedicated clock inputs are directly connected to internal clock buffers, there is no need to instantiate the clock buffer in the verilog code (although it doesn't hurt). Further, in order to even use a global clock buffer, you might have to bring the clock in on one of these special clock inputs. There's no getting around a careful look at the documentation regarding clocking requirements for the specific FPGA you intend to use.

Many newer synthesis tools will attempt to recognize clock signals that could do with a clock buffer and will automatically insert them for you (again, it doesn't hurt, and can only help, to make a direct instantiation).

A last word about clock distribution: newer, large FPGAs include increasingly complex clock routing and buffering resources. Particularly, due to the vast size and enormous quantity of potential loads, many large FPGAs include clocking subsections. These "regions" (often a quadrant of the die) host their own dedicated buffers and routes, where delay and skew can be reduced below what is possible for the global clocks (which are still available) that reach across the entire device. Some devices even include an even smaller sub-section. Often called "local clocks," these sub-areas are usually located along the periphery of the die and are associated with time-critical external interfaces.

The downside to this clocking sophistication is that when using these regional and local clocks, you introduce inherent partitioning to your design. You now have to be careful that all the logic associated with one of these sub-clocks can fit within the resources available in the sub-area, and more problematic, that all the logic can actually be *placed* by the complier in the sub-area. Conflicts arise, for example, when a signal that should be part of this sub-area is fed from or drives an external pin that is located in a different sub-area.

So far, we have looked at clock distribution that is sourced directly from an external clock. This is a common application, particularly where a single clock suffices for the logic operation, and the speeds are moderate enough that external signals can be clocked into and out of the FPGA with sufficient setup and hold times—up to perhaps 100 MHz. When the clocking structure and/or speeds extend beyond this, most FPGAs provide integrated PLL (Phase-Locked Loop) and/or DLL (Delay-Locked Loop) blocks that provide the resources needed for clock synthesis. PLL/DLLs provide the following functions in their role as the clock synthesis foundation, which we'll get to in turn:

- o phase alignment;

- o phased clock sets;

o frequency multiplication.

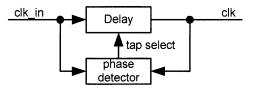

We start with the DLLs, the simpler of the two synthesis functions. The delay in the diagram below is just that, except that it consists of a series of precise delay elements, from which the propagating clock signal can be tapped as "clk." The phase detector compares the phases (relative edges) at the input and output of the delay, and can select the delay tap that creates the desired phase offset. Thus, for example, we could choose a slightly negative phase offset (i.e., something less than 360 degrees) so that "clk" is effectively moved back in time. Then it could incur propagation delay in the FPGA and be back to approximately where it was coming in as "clk\_in." The clock edges at the FPGA's internal registers would be (approximately) synchronized with those on the circuit board.

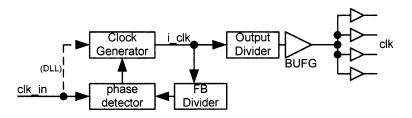

Simple DLL

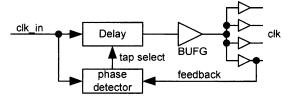

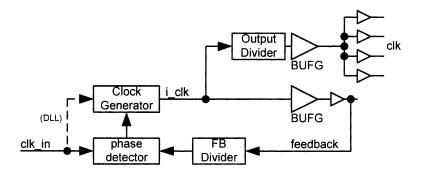

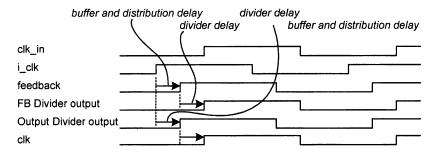

But we can do better than this. Using the feedback path, we can arrange for the locked loop to automatically compensate for the internal propagation delays. If the phase detector in the following diagram were set to find a zero-degree phase difference, then it would select a delay tap accordingly. No matter how much delay is introduced between the delay and "clk," the internal clock would always be precisely in phase with the input clock (to within the quantum margins of the taps).

#### **Propagation Compensated DLL**

Thus, we have achieved the first point above: phase alignment.

Now imagine that we have multiple delay/phase detector sets. Suppose that the first is configured to select a tap to achieve phase alignment as described above, but the rest are slaved to the first, whereby each produces a version of "clk" that has a fixed (and convenient) phase offset—say, 90, 180, and 270 degrees. This is exactly what we often need in very high-speed designs—DDR and QDR memory interfaces, for example.

That knocks off the second point: phased clock sets.