# **Embedded Systems Design with Platform FPGAs**

This page intentionally left blank

# Embedded Systems Design with Platform FPGAs Principles and Practices

Ron Sass Andrew G. Schmidt

Acquiring Editor: Todd Green Development Editor: Nate McFadden Project Manager: André Cuello Designer: Alisa Andreola

Morgan Kaufmann Publishers is an imprint of Elsevier. 30 Corporate Drive, Suite 400, Burlington, MA 01803, USA

This book is printed on acid-free paper.

Copyright © 2010, Elsevier Inc. All rights reserved.

No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or any information storage and retrieval system, without permission in writing from the publisher. Details on how to seek permission, further information about the Publisher's permissions policies and our arrangements with organizations such as the Copyright Clearance Center and the Copyright Licensing Agency, can be found at our Web site: www.elsevier.com/permissions.

This book and the individual contributions contained in it are protected under copyright by the Publisher (other than as may be noted herein).

#### Notices

Knowledge and best practice in this field are constantly changing. As new research and experience broaden our understanding, changes in research methods, professional practices, or medical treatment may become necessary.

Practitioners and researchers must always rely on their own experience and knowledge in evaluating and using any information, methods, compounds, or experiments described herein. In using such information or methods they should be mindful of their own safety and the safety of others, including parties for whom they have a professional responsibility.

To the fullest extent of the law, neither the Publisher nor the authors, contributors, or editors assume any liability for any injury and/or damage to persons or property as a matter of product liability, negligence or otherwise, or from any use or operation of any methods, products, instructions, or ideas contained in the material herein.

#### Library of Congress Cataloging-in-Publication Data

Sass, Ronald (Ronald R.)

Embedded systems design with platform FPGAs: Principles and Practices / Ronald Sass.

Includes bibliographical references.

ISBN 978-0-12-374333-6

1. Embedded computer systems. 2. Field programmable gate arrays. I. Title.

TK7895.E42S27 2010

004.16-dc22

2010010632

#### **British Library Cataloguing-in-Publication Data**

A catalogue record for this book is available from the British Library.

For information on all Morgan Kaufmann publications visit our Web site at www.mkp.com or www.elsevierdirect.com

Printed in the United States of America 10 11 12 13 5 4 3 2 1

Typeset by: diacriTech, India

# Working together to grow libraries in developing countries

www.elsevier.com | www.bookaid.org | www.sabre.org

**ELSEVIER**

BOOK AID International

Sabre Foundation

# **CONTENTS**

| Pre  | face   |                                             | . xi |

|------|--------|---------------------------------------------|------|

| Ack  | nowle  | dgments                                     | . XV |

| Chap |        | Introduction                                | 1    |

| 1.1  | Embe   | edded Systems                               | 3    |

|      | 1.1.1  | Embedded and General-Purpose                | 4    |

|      | 1.1.2  | Hardware, Software, and FPGAs               | 6    |

|      | 1.1.3  | Execution Models                            | 7    |

| 1.2  | Desig  | ın Challenges                               | 10   |

|      | 1.2.1  | Design Life Cycle                           | 10   |

|      | 1.2.2  | Measures of Success                         | 12   |

|      | 1.2.3  | Costs                                       | 17   |

| 1.3  | Platfo | orm FPGAs                                   | 20   |

|      | Chap   | ter in Review                               | 23   |

| 1.A  | Spect  | trometer Example                            | 25   |

|      | 1.A.1  | Scenario                                    | 25   |

|      | 1.A.2  | Two Solutions                               | 25   |

|      | 1.A.3  | Discussion                                  | 26   |

| 1.B  | Introd | ducing the Platform FPGA Tool Chain         | 27   |

|      | 1.B.1  | Getting Started with Xilinx Platform Studio | 28   |

|      | 1.B.2  | Using Xilinx Platform Studio                | 29   |

|      | Exerc  | sises                                       | 41   |

|      | Refer  | ences                                       | 42   |

| Chap | ter 2  | The Target                                  | 43   |

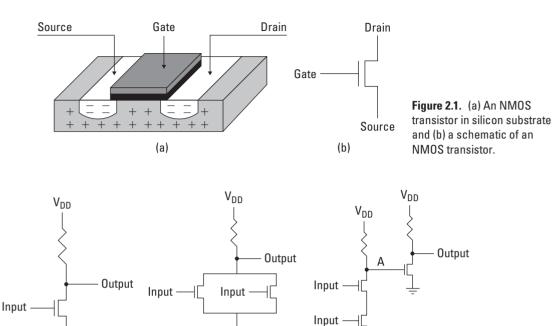

| 2.1  |        | S Transistor                                | 44   |

| 2.2  |        | ammable Logic Devices                       | 47   |

| 2.3  | _      | Programmable Gate Array                     | 49   |

| 2.0  | 2.3.1  | Function Generators                         | 49   |

|      | 2.3.2  | Storage Elements                            | 51   |

|      | 2.3.3  | Logic Cells                                 | 51   |

|      | 2.3.4  | Logic Blocks                                | 52   |

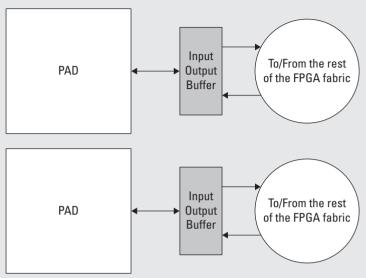

|      | 2.3.5  | Input/Output Blocks                         | 53   |

|      | 2.3.6  | Special-Purpose Function Blocks             | 53   |

| 2.4 | Hardy          | ware Description Languages       | 57  |

|-----|----------------|----------------------------------|-----|

|     | 2.4.1          | VHDL                             | 58  |

|     | 2.4.2          | Verilog                          | 68  |

|     | 2.4.3          | Other High-Level HDLs            | 73  |

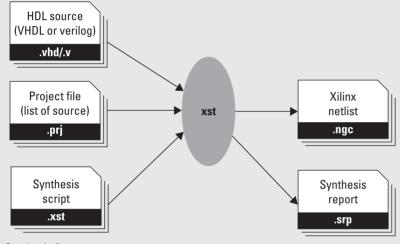

| 2.5 | From           | HDL to Configuration Bitstream   |     |

|     |                | ter in Review                    | 78  |

| 2.A |                | Virtex 5                         | 81  |

|     | 2.A.1          |                                  | 82  |

|     | 2.A.2          | ·                                | 82  |

|     | 2.A.3          | Configurable Logic Block         |     |

|     | 2.A.4          | Block RAM                        | 83  |

|     | 2.A.5          | DSP Slices                       |     |

|     | 2.A.6          | Select I/O                       | 85  |

|     | 2.A.7          | High-Speed Serial Transceivers   | 85  |

|     | 2.A.8          | e ·                              |     |

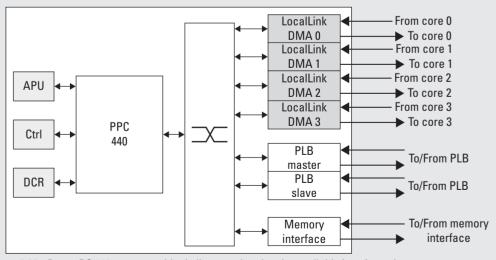

|     | 2.A.9          | PowerPC 440                      | 87  |

| 2.B |                | Integrated Software Environment  |     |

|     |                | Overview of Commands             |     |

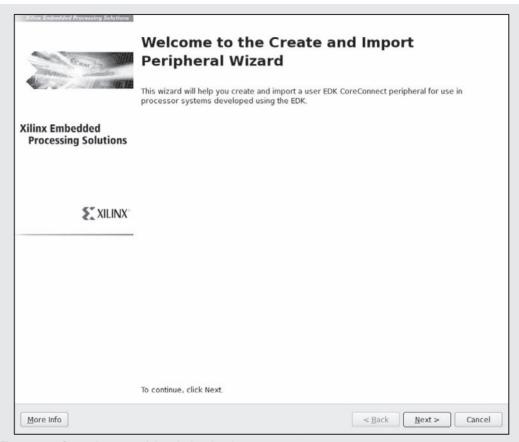

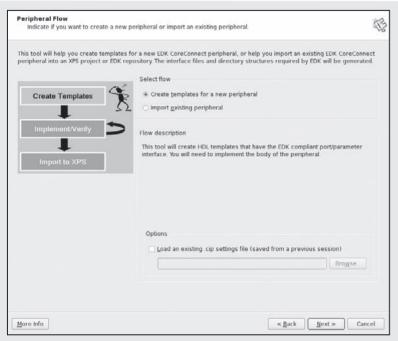

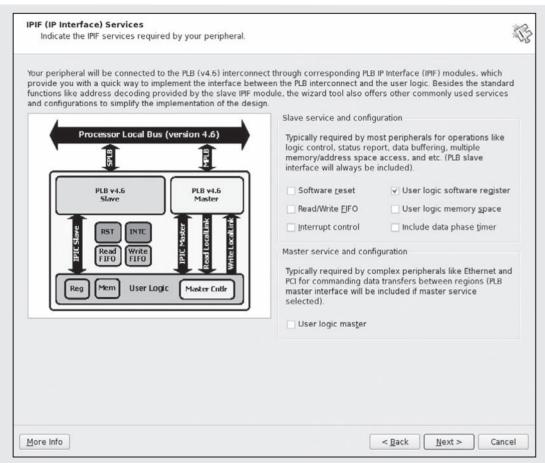

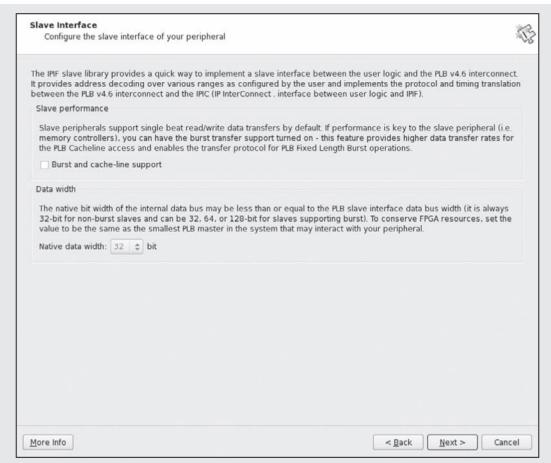

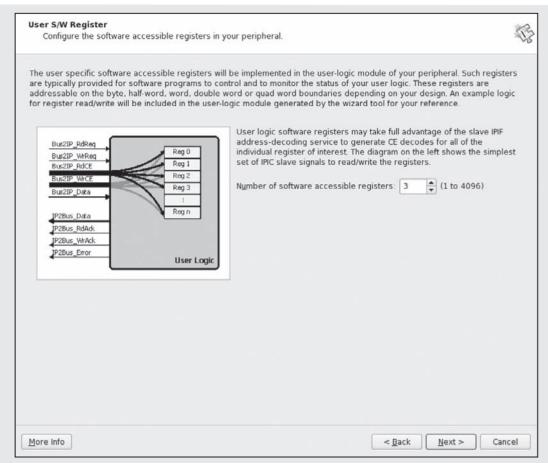

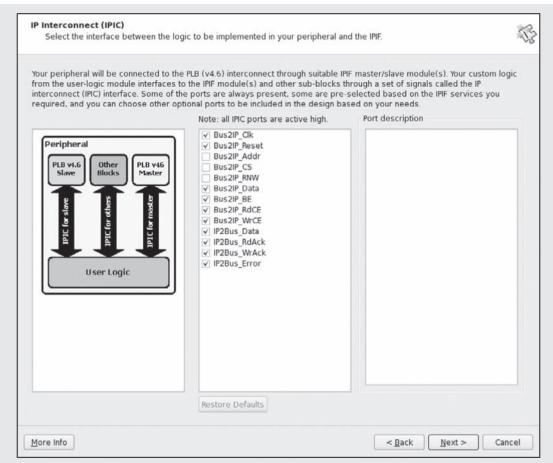

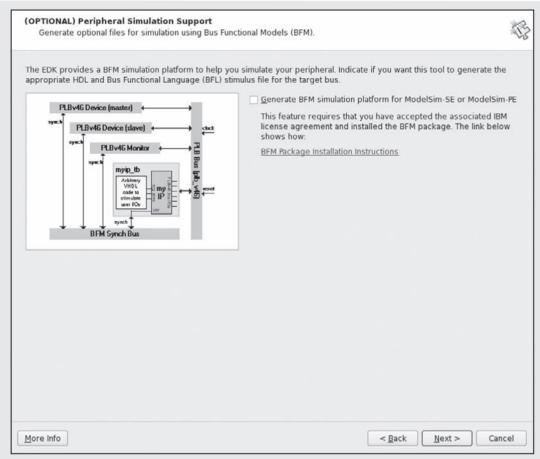

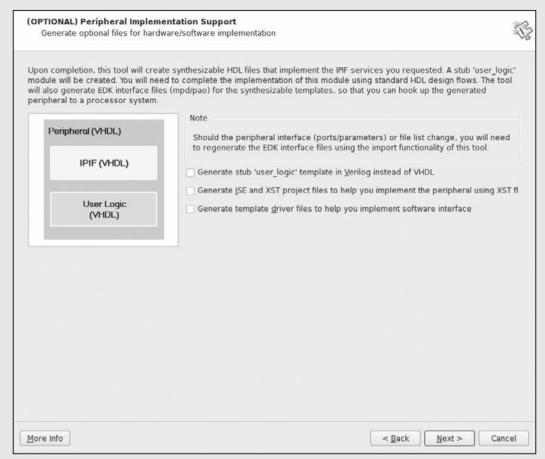

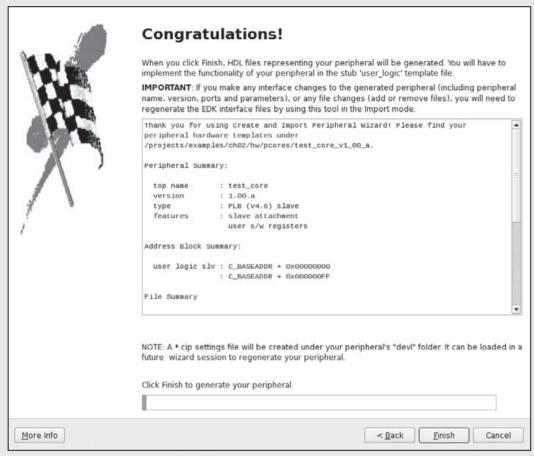

| 2.C | Creat          | ing and Generating Custom IP     | 94  |

|     | 2.C.1          |                                  | 94  |

|     | 2.C.2          |                                  |     |

|     | 2.C.3          | Hardware Core Project Directory  | 105 |

|     | Exerc          | ises                             | 111 |

|     | Refer          | ences                            | 112 |

|     |                |                                  |     |

|     |                | System Design                    |     |

| 3.1 |                | ples of System Design            |     |

|     | 3.1.1          | Design Quality                   |     |

|     | 3.1.2          | Modules and Interfaces           |     |

|     | 3.1.3          | Abstraction and State            |     |

|     | 3.1.4          | Cohesion and Coupling            |     |

|     | 3.1.5          | Designing for Reuse              |     |

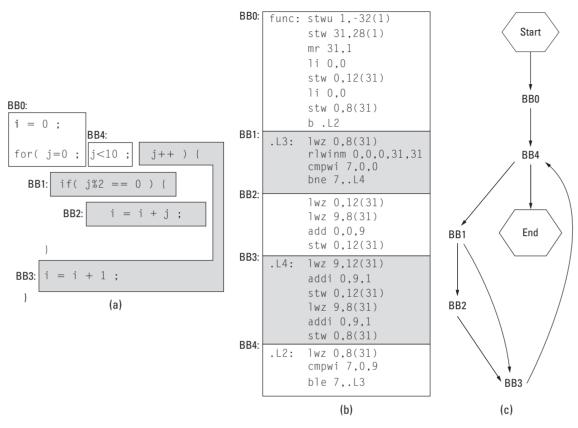

|     |                | ol Flow Graph                    |     |

| 3.3 |                | ware Design                      |     |

|     | 3.3.1          | Origins of Platform FPGA Designs |     |

|     | 3.3.2          | Platform FPGA Components         |     |

|     | 3.3.3          | Adding to Platform FPGA Systems  |     |

| 0 1 | 3.3.4          | Assembling Custom Compute Cores  |     |

| 3.4 |                | vare Design                      |     |

|     | シルコ            | System Software Untions          | 154 |

|     | 3.4.1<br>3.4.2 | System Software Options          |     |

|       | 3.4.3         | Cross-Development Tools                         | 158 |

|-------|---------------|-------------------------------------------------|-----|

|       | 3.4.4         | Monitors and Bootloader                         | 159 |

|       | Chapt         | ter in Review                                   | 161 |

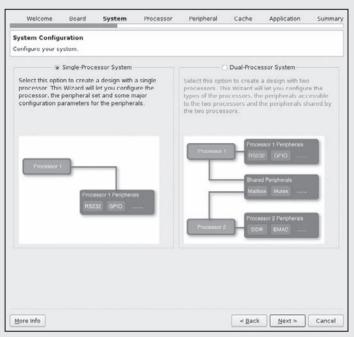

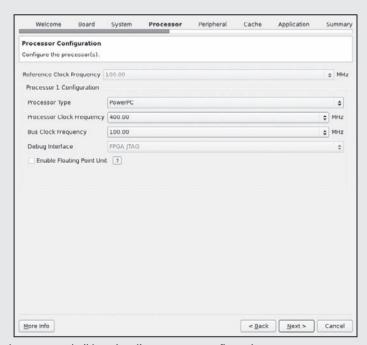

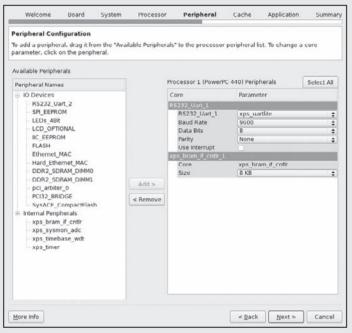

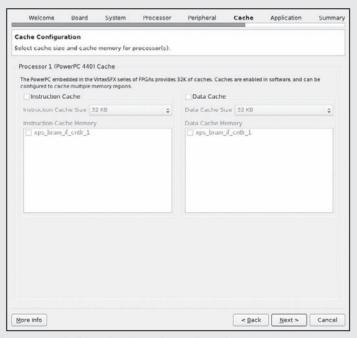

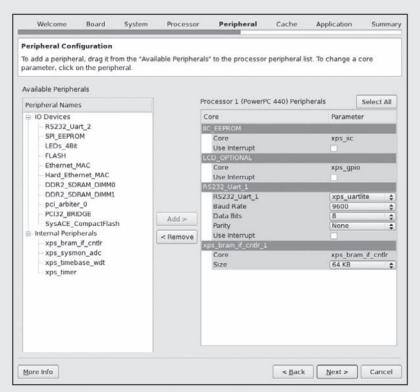

| 3.A   | Platfo        | orm FPGA Architecture Design                    | 162 |

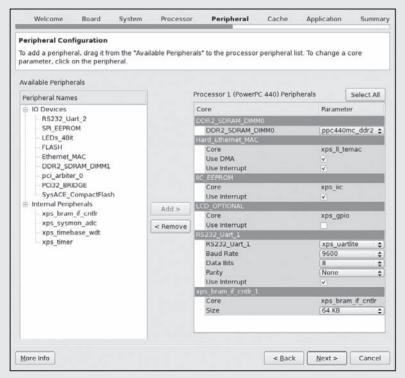

|       |               | Xilinx EDK and IBM CoreConnect                  |     |

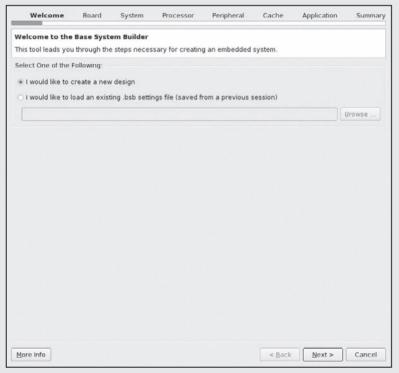

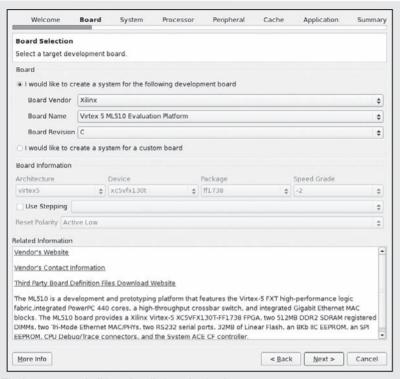

|       | 3.A.2         | Building Base Systems                           | 166 |

|       | 3.A.3         | Augmenting Base Systems                         | 167 |

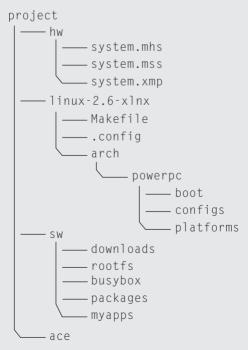

|       | 3.A.4         | XPS Project Files                               |     |

|       | 3.A.5         | Practical Example: Floating-Point Adder         | 169 |

|       | 3.A.6         | Base System                                     |     |

|       | 3.A.7         | · · ·                                           |     |

|       |               | Core Generator                                  |     |

|       |               | User Logic                                      |     |

|       |               | Modify Hardware Core Project Files              |     |

|       |               | Connecting the Hardware Core to the Base System |     |

|       |               | ? Testing the System                            |     |

| 3.B   |               | edded GNU/Linux System                          |     |

|       | 3.B.1         | 3 3 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1         |     |

|       | 3.B.2         | <b>3</b>                                        |     |

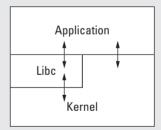

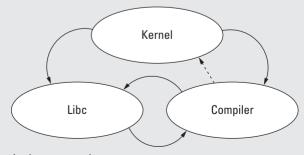

|       | 3.B.3         | Cross-Development Tools and Libraries           |     |

|       | 3.B.4         | Cross-Compiling Linux                           |     |

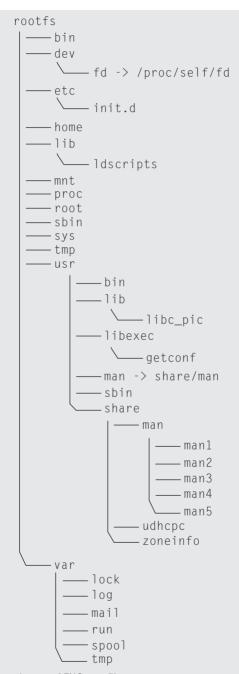

|       | 3.B.5         | Building a Root Filesystem                      |     |

|       | 3.B.6         | Booting Linux on the ML510                      |     |

|       |               | ises                                            |     |

|       | Refer         | ences                                           | 195 |

|       |               |                                                 |     |

|       |               |                                                 |     |

| Chapt |               | Partitioning                                    |     |

| 4.1   | Overv         | view of Partitioning Problem                    | 198 |

| 4.2   | Analy         | tical Solution to Partitioning                  | 201 |

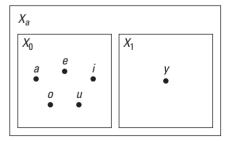

|       | 4.2.1         | Basic Definitions                               | 202 |

|       | 4.2.2         | Expected Performance Gain                       |     |

|       | 4.2.3         | Resource Considerations                         |     |

|       | 4.2.4         | Analytical Approach                             | 209 |

| 4.3   | Communication |                                                 | 211 |

|       | 4.3.1         | Invocation/Coordination                         |     |

|       | 4.3.2         | Transfer of State                               | 218 |

| 4.4   | Practi        | ical Issues                                     | 223 |

|       | 4.4.1         | Profiling Issues                                | 223 |

|       | 4.4.2         | Data Structures                                 |     |

|       | 4.4.3         | Manipulate Feature Size                         | 228 |

|       | Chapt   | ter in Review                          | 228  |

|-------|---------|----------------------------------------|------|

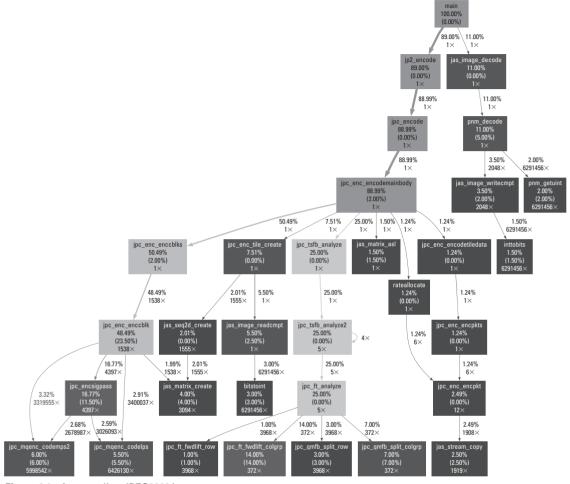

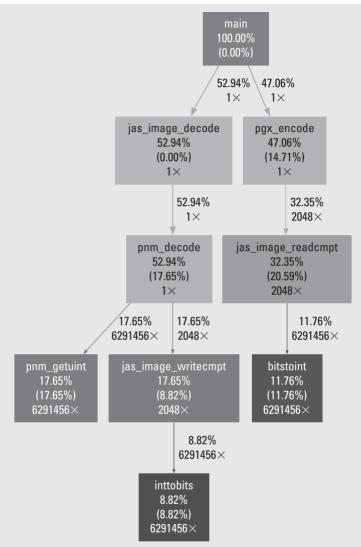

| 4.A   | Profili | ing with Gprof                         | 229  |

|       |         | Kernel                                 |      |

|       | 4.B.1   | Kernel Modules                         |      |

|       | 4.B.2   | Address Spaces                         | 236  |

|       | 4.B.3   | Application View                       |      |

|       | 4.B.4   | Char Device Driver                     |      |

|       | 4.B.5   | Summary                                | 241  |

|       | Exerc   | ises                                   | 242  |

|       | Refer   | ences                                  | 245  |

| Chan  | tor 5   | Spatial Design                         | 2/17 |

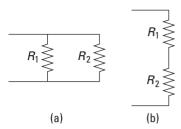

| 5.1   |         | ples of Parallelism                    |      |

| 5.1   | 5.1.1   | Granularity                            |      |

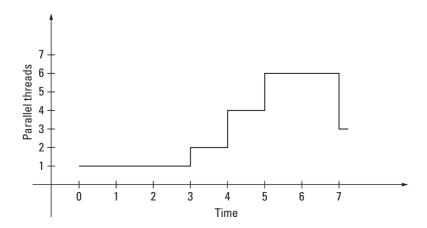

|       | 5.1.1   | Degree of Parallelism                  |      |

|       | 5.1.3   | •                                      |      |

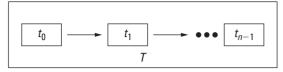

| 5.2   |         | ifying Parallelism                     |      |

| ٥.۷   | 5.2.1   | Ordering                               |      |

|       | 5.2.2   | Dependence                             |      |

|       | 5.2.3   | Uniform Dependence Vectors             |      |

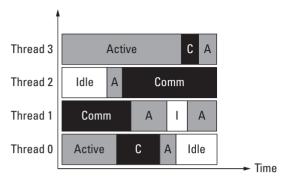

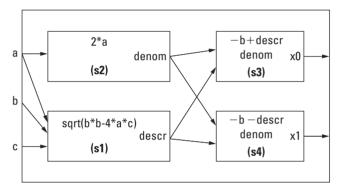

| 5.3   |         | al Parallelism with Platform FPGAs     |      |

|       | 5.3.1   | Parallelism within FPGA Hardware Cores |      |

|       | 5.3.2   |                                        |      |

|       | Chapt   | ter in Review                          |      |

| 5.A   |         | ıl VHDL Topics for Spatial Design      |      |

|       |         | Constants and Generics                 |      |

|       | 5.A.2   | User-Defined Types                     | 276  |

|       | 5.A.3   | Generate Statements                    | 278  |

|       | 5.A.4   | Design Constraints                     |      |

| 5.B   | Debu    | gging Platform FPGA Designs            | 280  |

|       | 5.B.1   |                                        |      |

|       | 5.B.2   | Software Addressable Registers         |      |

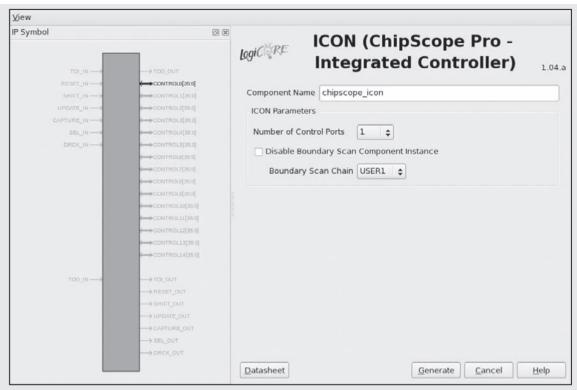

|       | 5.B.3   | Xilinx ChipScope                       |      |

|       |         | ises                                   |      |

|       | Refer   | ences                                  | 293  |

| Chant | ter 6   | Managing Bandwidth                     | 295  |

| 6.1   | Balan   | icing Bandwidth                        | 296  |

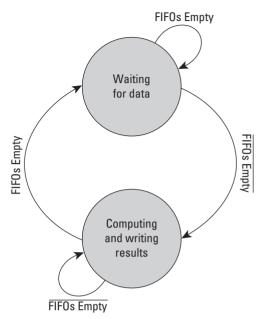

| 0.1   |         | Kahn Process Network                   |      |

|       |         |                                        |      |

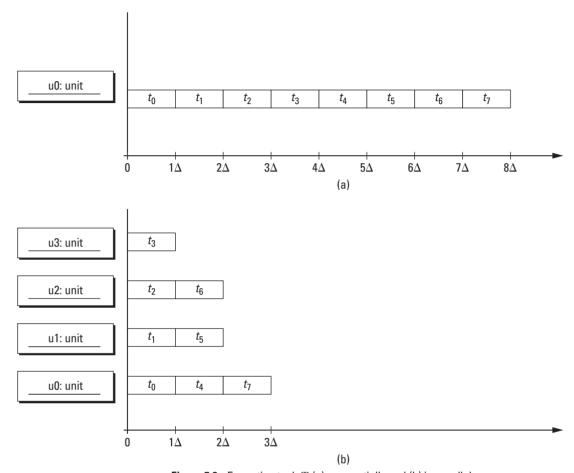

|       | 6.1.2                                                                                                                                 | Synchronous Design                                                                                                                                                                                                                                                             | 300                                                                              |

|-------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|       | 6.1.3                                                                                                                                 | Asynchronous Design                                                                                                                                                                                                                                                            | 300                                                                              |

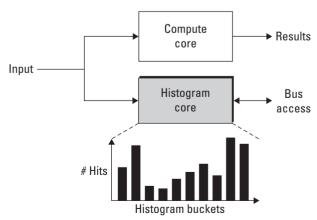

| 6.2   | Platfo                                                                                                                                | orm FPGA Bandwidth Techniques                                                                                                                                                                                                                                                  | 300                                                                              |

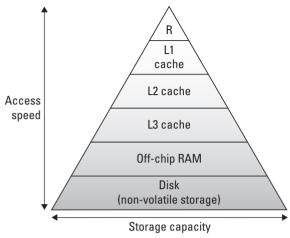

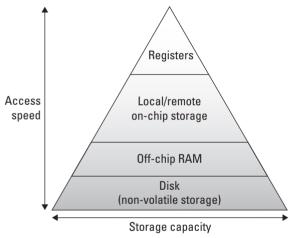

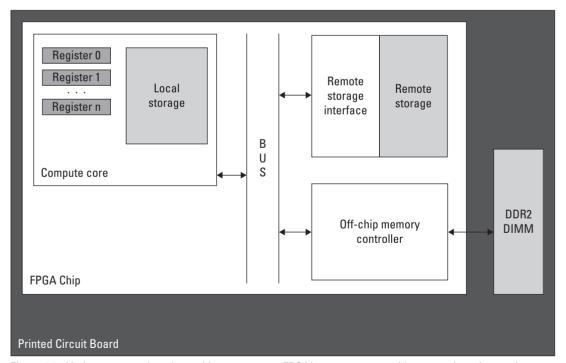

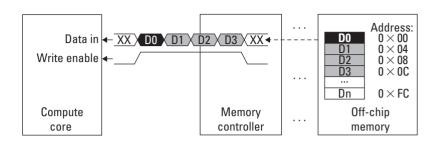

|       | 6.2.1                                                                                                                                 | On-Chip and Off-Chip Memory                                                                                                                                                                                                                                                    | 301                                                                              |

|       | 6.2.2                                                                                                                                 | Streaming Instrument Data                                                                                                                                                                                                                                                      | 313                                                                              |

|       | 6.2.3                                                                                                                                 | Practical Issues                                                                                                                                                                                                                                                               | 316                                                                              |

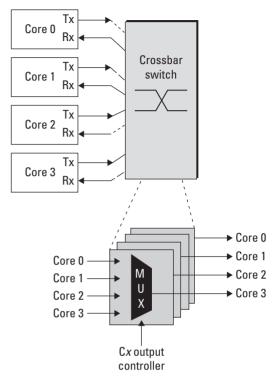

| 6.3   | Scala                                                                                                                                 | ble Designs                                                                                                                                                                                                                                                                    | 317                                                                              |

|       | 6.3.1                                                                                                                                 | Scalability Constraints                                                                                                                                                                                                                                                        |                                                                                  |

|       | 6.3.2                                                                                                                                 | Scalability Solutions                                                                                                                                                                                                                                                          |                                                                                  |

|       | Chapt                                                                                                                                 | ter in Review                                                                                                                                                                                                                                                                  | 324                                                                              |

| 6.A   | On-Cl                                                                                                                                 | nip Memory Access                                                                                                                                                                                                                                                              | 326                                                                              |

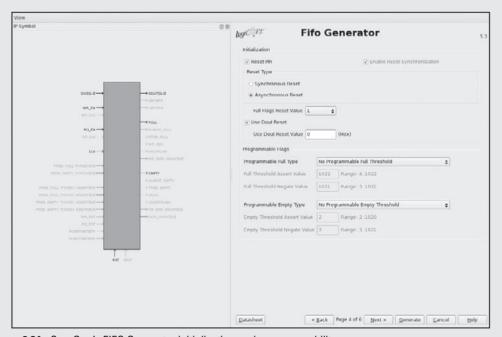

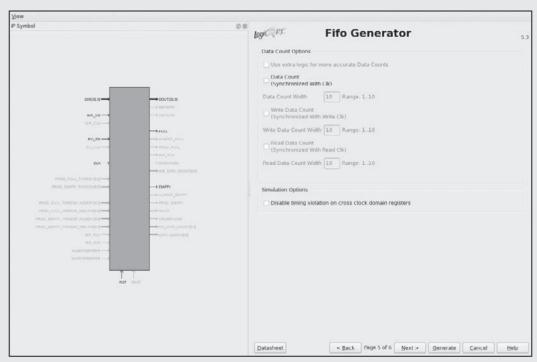

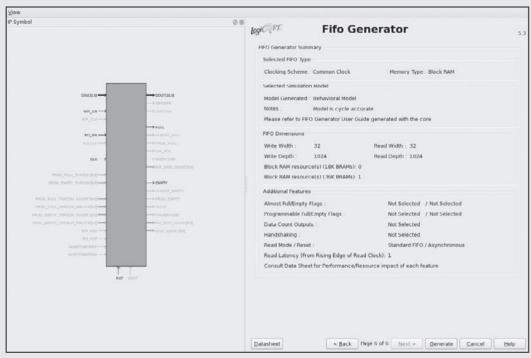

|       |                                                                                                                                       | FIFOs                                                                                                                                                                                                                                                                          |                                                                                  |

|       | 6.A.2                                                                                                                                 | Block RAM                                                                                                                                                                                                                                                                      | 328                                                                              |

|       | 6.A.3                                                                                                                                 | LocalLink Interface                                                                                                                                                                                                                                                            | 328                                                                              |

| 6.B   | Off-C                                                                                                                                 | hip Memory Access                                                                                                                                                                                                                                                              | 330                                                                              |

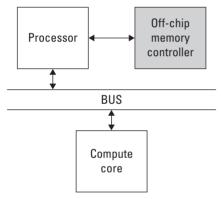

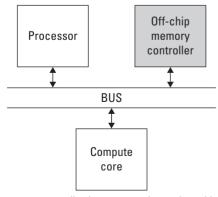

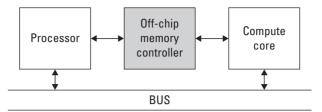

|       | 6.B.1                                                                                                                                 | - 0                                                                                                                                                                                                                                                                            |                                                                                  |

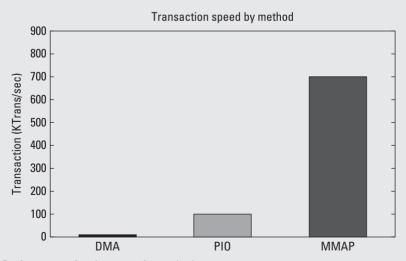

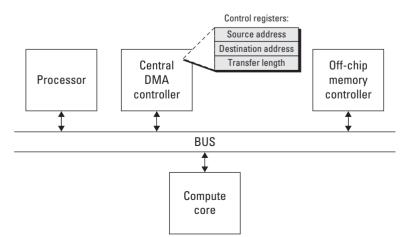

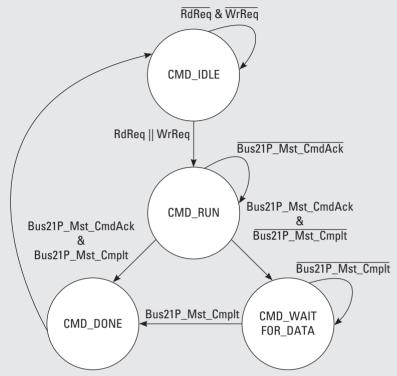

|       | 6.B.2                                                                                                                                 | Central DMA Controller                                                                                                                                                                                                                                                         | 330                                                                              |

|       | 6.B.3                                                                                                                                 | Bus Master                                                                                                                                                                                                                                                                     |                                                                                  |

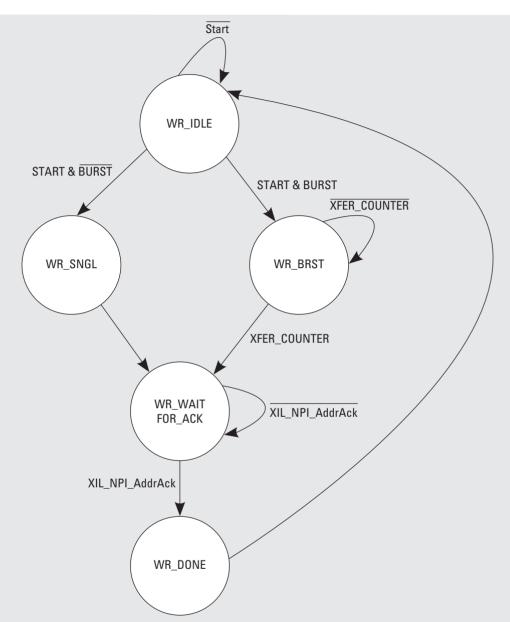

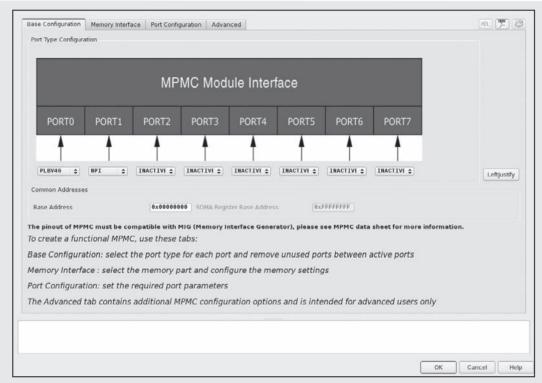

|       | 6.B.4                                                                                                                                 | Native Port Interface                                                                                                                                                                                                                                                          |                                                                                  |

|       | Exerc                                                                                                                                 | ises                                                                                                                                                                                                                                                                           | 346                                                                              |

|       | Refer                                                                                                                                 | ences                                                                                                                                                                                                                                                                          | 346                                                                              |

|       |                                                                                                                                       |                                                                                                                                                                                                                                                                                |                                                                                  |

|       |                                                                                                                                       |                                                                                                                                                                                                                                                                                |                                                                                  |

| Chant | tor 7                                                                                                                                 | Outeido World                                                                                                                                                                                                                                                                  | 2/17                                                                             |

|       | ter 7                                                                                                                                 |                                                                                                                                                                                                                                                                                |                                                                                  |

|       | Point-                                                                                                                                | to-Point Communication                                                                                                                                                                                                                                                         | 348                                                                              |

|       | Point-<br>7.1.1                                                                                                                       | to-Point Communication                                                                                                                                                                                                                                                         | 348<br>349                                                                       |

| 7.1   | Point-<br>7.1.1<br>7.1.2                                                                                                              | to-Point Communication RS-232 Other Low-Speed Communication                                                                                                                                                                                                                    | 348<br>349<br>350                                                                |

| 7.1   | Point-<br>7.1.1<br>7.1.2<br>Intern                                                                                                    | to-Point Communication                                                                                                                                                                                                                                                         | 348<br>349<br>350<br>350                                                         |

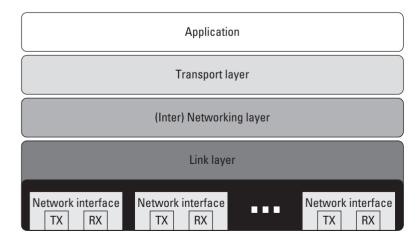

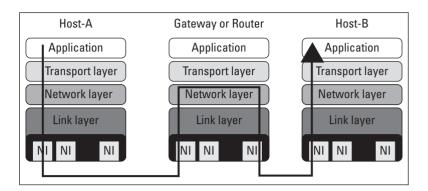

| 7.1   | Point-<br>7.1.1<br>7.1.2<br>Intern<br>7.2.1                                                                                           | to-Point Communication RS-232 Other Low-Speed Communication networking Communication Concepts                                                                                                                                                                                  | 348<br>349<br>350<br>350<br>350                                                  |

| 7.1   | Point-<br>7.1.1<br>7.1.2<br>Interr<br>7.2.1<br>7.2.2                                                                                  | to-Point Communication RS-232 Other Low-Speed Communication networking Communication Concepts Application Interface                                                                                                                                                            | 348<br>349<br>350<br>350<br>350<br>355                                           |

| 7.1   | Point-<br>7.1.1<br>7.1.2<br>Interr<br>7.2.1<br>7.2.2<br>7.2.3                                                                         | to-Point Communication RS-232 Other Low-Speed Communication networking Communication Concepts Application Interface Higher Level Protocols                                                                                                                                     | 348<br>349<br>350<br>350<br>350<br>355<br>358                                    |

| 7.1   | Point-<br>7.1.1<br>7.1.2<br>Interr<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4                                                                | to-Point Communication RS-232 Other Low-Speed Communication networking Communication Concepts Application Interface Higher Level Protocols Operating System Configuration                                                                                                      | 348<br>349<br>350<br>350<br>355<br>358<br>362                                    |

| 7.1   | Point-<br>7.1.1<br>7.1.2<br>Intern<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>Chapt                                                       | to-Point Communication RS-232 Other Low-Speed Communication networking Communication Concepts Application Interface Higher Level Protocols Operating System Configuration                                                                                                      | 348<br>349<br>350<br>350<br>350<br>355<br>358<br>362<br>363                      |

| 7.1   | Point-<br>7.1.1<br>7.1.2<br>Intern<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>Chapt<br>High-                                              | to-Point Communication RS-232 Other Low-Speed Communication etworking Communication Concepts Application Interface Higher Level Protocols Operating System Configuration ter in Review Speed Serial Communication                                                              | 348<br>349<br>350<br>350<br>355<br>358<br>362<br>363<br>365                      |

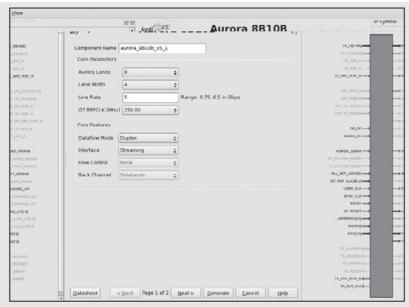

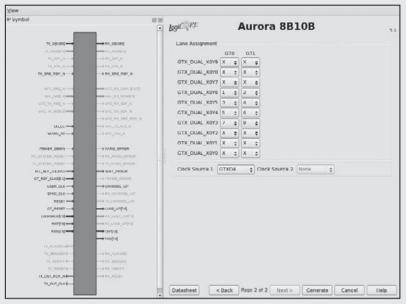

| 7.1   | Point-<br>7.1.1<br>7.1.2<br>Intern<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>Chapt<br>High-<br>7.A.1                                     | to-Point Communication RS-232 Other Low-Speed Communication networking Communication Concepts Application Interface Higher Level Protocols Operating System Configuration ter in Review Speed Serial Communication RocketlO                                                    | 348<br>349<br>350<br>350<br>355<br>358<br>362<br>363<br>365<br>365               |

| 7.1   | Point-<br>7.1.1<br>7.1.2<br>Intern<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>Chapt<br>High-<br>7.A.1<br>7.A.2                            | to-Point Communication RS-232 Other Low-Speed Communication networking Communication Concepts Application Interface Higher Level Protocols Operating System Configuration ter in Review Speed Serial Communication RocketlO Aurora Example                                     | 348<br>349<br>350<br>350<br>355<br>362<br>363<br>365<br>365<br>365               |

| 7.1   | Point-<br>7.1.1<br>7.1.2<br>Intern<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>Chapt<br>High-<br>7.A.1<br>7.A.2<br>7.A.3                   | to-Point Communication RS-232 Other Low-Speed Communication networking Communication Concepts Application Interface Higher Level Protocols Operating System Configuration ter in Review Speed Serial Communication RocketlO Aurora Example LocalLink Interface                 | 348<br>349<br>350<br>350<br>355<br>363<br>363<br>365<br>365<br>365<br>366        |

| 7.1   | Point-<br>7.1.1<br>7.1.2<br>Intern<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>Chapt<br>High-<br>7.A.1<br>7.A.2                            | to-Point Communication RS-232 Other Low-Speed Communication etworking Communication Concepts Application Interface Higher Level Protocols Operating System Configuration ter in Review Speed Serial Communication RocketlO Aurora Example LocalLink Interface Clock Correction | 348<br>349<br>350<br>350<br>355<br>363<br>365<br>365<br>365<br>366<br>366        |

| 7.1   | Point-<br>7.1.1<br>7.1.2<br>Intern<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>Chapt<br>High-<br>7.A.1<br>7.A.2<br>7.A.3<br>7.A.4<br>7.A.5 | to-Point Communication RS-232 Other Low-Speed Communication networking Communication Concepts Application Interface Higher Level Protocols Operating System Configuration ter in Review Speed Serial Communication RocketlO Aurora Example LocalLink Interface                 | 348<br>349<br>350<br>350<br>355<br>363<br>365<br>365<br>365<br>366<br>366<br>367 |

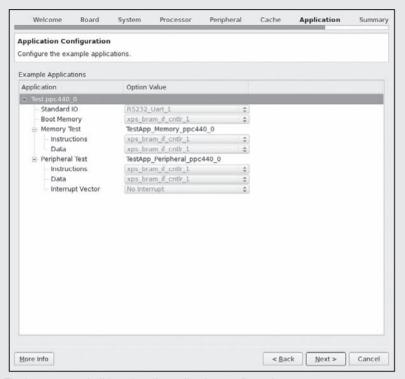

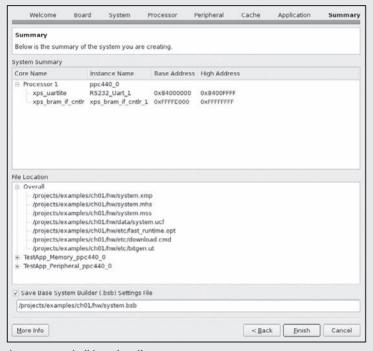

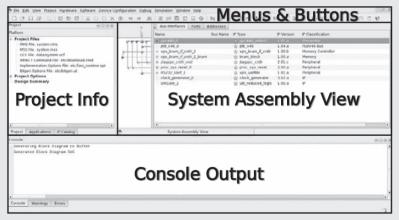

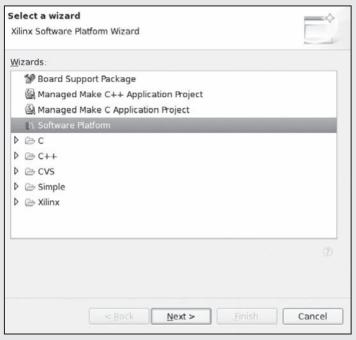

|      |         | Generating the Hardware Base System |     |

|------|---------|-------------------------------------|-----|

|      |         | Testing the Design                  |     |

|      |         | isesences                           |     |

|      | neiere  | ences                               | 3/4 |

| Glo  | ssary . |                                     | 375 |

| Inde | ex      |                                     | 381 |

# **PREFACE**

Xilinx, Inc. introduced the Field-Programmable Gate Array (FPGA) in 1984 as an advanced programmable logic device. It is now part of a multi-billion dollar market and FPGAs have made their way into products as diverse as digital cameras, automobiles, and network switches that drive the Internet. FPGAs have even flown to Mars (Ratter, 2004).

Almost since its inception, people have recognized the potential of using these devices to build custom computing architectures, but to date the market is overwhelmingly "glue logic" and prototyping. Nonetheless, advances in process technology have yielded modern FPGAs with very large capacities and a wide range of features built into the chip. The confluence of these features — which include multiple processors, large amounts of memory, hundreds of multipliers, and high-speed I/O — have reached a critical mass: now more than ever, Platform FPGAs are poised to realize a more prominent role in computing systems.

This ability to deploy sophisticated computing systems on a single FPGA device is likely to make a significant impact on embedded computing systems. While small (indeed tiny) 8 and 16 bit computing systems are and will remain a very important segment of the embedded systems market, trends over the last several years suggest that the use of standard, off-the-shelf 32-bit processors for embedded systems is growing fast. These higher-end embedded systems come with high levels of integration, often incorporating a significant portion of the system on a (fixed and manufactured) chip. There are many benefits to this level of integration but one significant drawback is that much of the system architecture is predetermined and may not be optimal for the particular targeted application. The alternative, developing a system architecture on a custom System-on-a-Chip (SoC), is too costly except for high volume (millions of units) products. When the application fits the resources provided, all is well. But oftentimes the application does not fit and some of the integrated resources are wasted while additional discrete hardware is required to make up the deficiency. With the Platform FPGA, engineers gain all of the advantages of integration but retain the flexibility to engineer a balanced system architecture on a per-application basis.

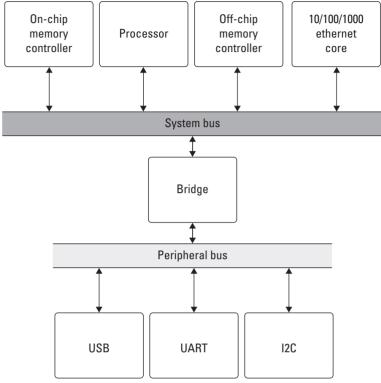

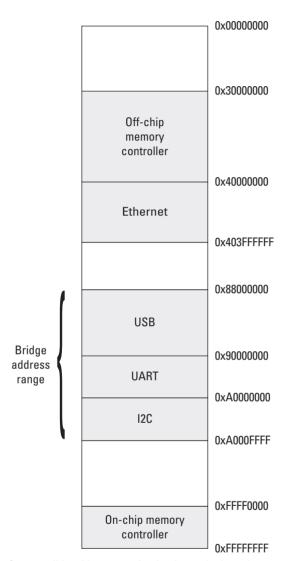

Armed with multiple kinds of buses, various direct communication links, bridges, I/O components, and an assortment of other special-purpose Intellectual Property cores, Platform FPGA designers can readily customize their system architecture. For example, with hundreds of distributed block RAMs, a designer can configure one large addressable memory, disperse the RAM throughout the system as individual buffers, or design some combination of the two. Application-specific functionality (i.e., custom hardware cores) can be designed and incorporated. Although Application-Specific Integrated Circuits (ASICs) will always outperform the identical FPGA implementation, the FPGA solution avoids the expense, risk, and time-to-market issues associated with manufacturing of an ASIC. The FPGA is a virtual blank slate giving the engineer the ability to provision the resources to best fit the application after the manufacture, test, and verification of the physical device. This flexibility increases efficiency of the system solution and every discrete component saved reduces cost and increases reliability.

Of course, there is a price to be paid for this enormous degree of hardware flexibility. In addition to compilers, debuggers, and other conventional software tools used for processorbased embedded system development, the Platform FPGA designer has to be fluent in hardware design and synthesis as well as system integration tools. Decisions that previously were largely constrained by architecture choice — such as how to partition the application between hardware and software — now have a much larger solution space. Beyond understanding the characteristics of a particular processor's system bus, the designer has to weigh the strengths and weaknesses of multiple communication mechanisms. Balancing complex networks of on-chip components presents a novel challenge for those used to working with predetermined architectures.

In many ways, these challenges embody computer engineering. However, until the Platform FPGA emerged, practical issues (such as the cost of building custom silicon solutions) made a hands-on study prohibitively expensive. Students learned computer system architecture from textbooks and conceptual models. The practical aspects of engineering custom computer systems from the ground up was typically the purview of a few specialists. Knowledge and practical tools — such as how to create a Board Support Package for an embedded system — was typically learned on the job.

The aim of this textbook is to introduce the reader to system development on a Platform FPGA. The focus is on embedded systems but it also serves as a general guide to building custom computing systems. The text describes the fundamental technology in terms of hardware, software, and a set of principles to guide the development of Platform FPGA systems. The goal is to show how to systematically and creatively apply these principles to construction of applicationspecific embedded system architectures. There is a strong focus on using Free and Open Source software to increase productivity.

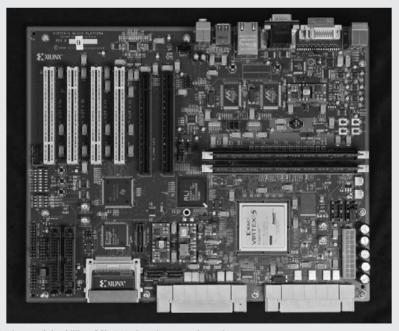

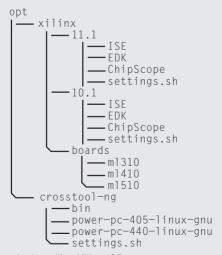

The organization of each chapter in the book includes two parts. The white pages describe concepts, principles, and general knowledge. The gray pages include a technical rendition of the main issues of the chapter and show the concepts applied in practice. This includes stepby-step details for a specific developer board and chain so that readers can carry out the same steps on their own. Rather than try to demonstrate the concepts on a broad set of tools and boards, the text uses a single set of tools (Xilinx Platform Studio, Linux, and GNU) throughout and uses single developer board (Xilinx ML-510) for the examples. The belief is that a single system, completely described, is more valuable to the reader than partial information about a range of systems.

#### How to Read This Book

This book was designed to make it easy for a number of different readers to quickly find the information they need. If you are an undergraduate with a software background who might not have had a course in electronics, the white pages in chapter two start with a basic transistor and describes how an FPGA — a solid state device — implements programmable hardware. If you are a practicing engineer with experience in embedded systems but are new to FPGAs, then reading just the blue pages will let you skip the theory and focus on the practical aspects of building Linux-based systems on an FPGA. If you are a student in a senior design course, the lectures probably focus on project management. You won't find that material here but you may find this text to be a handy practical guide to complete your project. On the other hand, if you have a very specific project involving cutting-edge technology, then you may not find that

particular topic covered in sufficient depth here. However, if you are looking to get started, need a general overview of the concepts, and still want enough step-by-step details to implement a real, working system this may prove to be the perfect text for you!

#### Note to Instructors

There are several roles this text may play in a typical computer curriculum. In many departments, a single embedded systems course is a technical elective offered to Seniors. The core material is delivered within the context of a substantial, semester-long project. This text provides a suitable introduction to embedded systems and — because it provides all of the practical material students need to carry-out their projects — the instructor has the freedom to introduce select topics in class. For curricula with a focus area in embedded systems (offering multiple technical electives), this text may be used to teach a course on reconfigurable computing. Such a course would complement a comprehensive embedded systems course that gives a full treatment of the area including small systems and an expanded description of real-time issues. Finally, the IEEE-CS/ACM Joint Task Force on Computing Curricula (Ironman Draft) includes as a basic computer engineering component a "culminating project." This often manifests itself in current curricula as a Senior Design or Capstone course. As such, the course draws together subjects taught independently in the curriculum and helps bridge the students' academic and professional careers. FPGAs serve exceedingly well (and are often used) in such a course. Their flexibility allows a wide range of potential projects and those projects necessarily encompass both hardware and software components: the essence of computer engineering. For that reason, many instructors may find this text to be an excellent resource for the students in their culminating project.

# Online Materials

Many of the commands, scripts, and URL links referenced in the text are included in the text. However, for the reader's convenience, the publisher maintains a Web site with all of these materials online including scripts too long to insert into the text. In addition to links pointing to the latest version of the open source software used in the text, the Web site also archives the exact (known to work) versions used in this text.

# Reference

Ratter, D. (2004). FPGAs on Mars. *Xcell Journal*, **Q3**(50), 8–11.

This page intentionally left blank

# **ACKNOWLEDGMENTS**

There have been many people that have contributed to this project and helped improve the book in numerous ways. We would like to acknowledge the current students in the Reconfigurable Computing Systems lab (University of North Carolina at Charlotte) for reading chapters and providing feedback – sometimes with very short notice. These include William V. Kritikos, Scott Buscemi, Bin Huang, Shanyuan Gao, Robin Jacob Pottathuparambil, Siddhartha Datta, Ashwin A. Mendon, Shweta Jain, Yamuna Rajasekhar, and Rahul R. Sharma. Other colleagues and previous students have also contributed; the authors would also like to thank Brian Greskamp (D.E. Shaw), Srinivas Beeravolu (Xilinx, Inc.), Parag Beeraka (AMD Inc.), and David Andrews (University of Arkansas) for their help. Many of the questions and examples have been adapted from our collaborations with these individuals. Several external reviewers provided valuable feedback. We would like to thank Roy Kravitz (Serveron, A Division of BPL Global), Duncan Buell (University of South Carolina), Cameron Patterson (Virginia Tech), and Jim Turley (Embedded Technology Journal). We would also like to thank the team at Morgan-Kaufmann; in particular, Nate McFadden and Andre Cuello, were instrumental in helping us complete the manuscript on time. Also, we would like to thank Xilinx — they encouraged us to start this project and then gave us the freedom to complete it as we saw fit. Finally, the authors would like to thank our families — Jennie, Joseph, and Hilary — for giving us the time to complete this project. You guys are the best!

This page intentionally left blank

# INTRODUCTION

**em**·**bed** — to make something an integral part of

Merriam-Webster Online

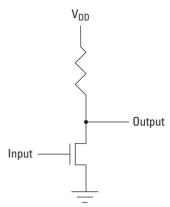

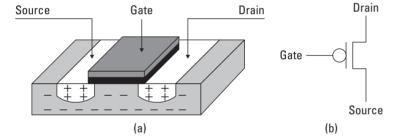

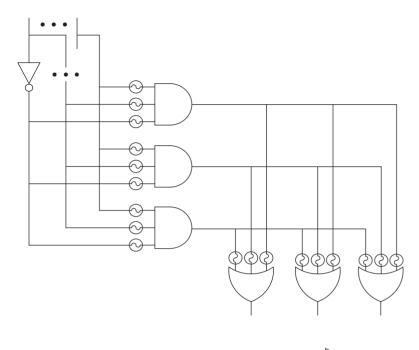

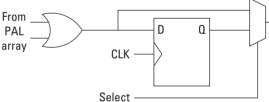

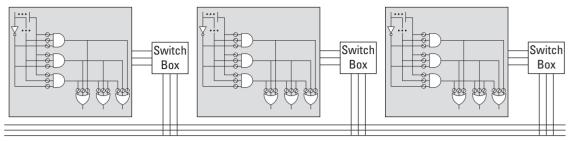

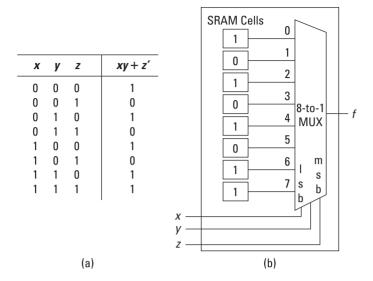

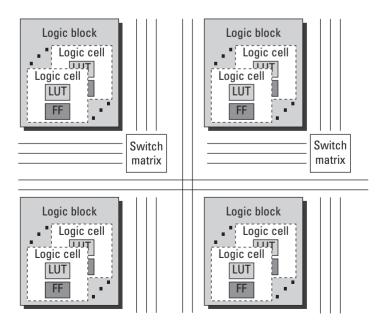

From smart phones to medical equipment, from microwaves to antilock braking systems — modern embedded systems projects develop computing machines that have become an integral part of our society. To develop these products, computer engineers employ a wide range of tools and technology to assemble embedded systems from hardware and software components. One component — the Field-Programmable Gate Array (FPGA) — is becoming increasingly important. Informally, an FPGA can be thought of as a "blank slate" on which any digital circuit can be configured (Figure 1.1). Moreover, the desired functionality can be configured in the field — that is, after the device has been manufactured, installed in a product, or, in some cases, even after the product has been shipped to the consumer. This makes the FPGA device fundamentally different from other Integrated Circuit (IC) devices. In short, an FPGA provides programmable "hardware" to the embedded systems developer.

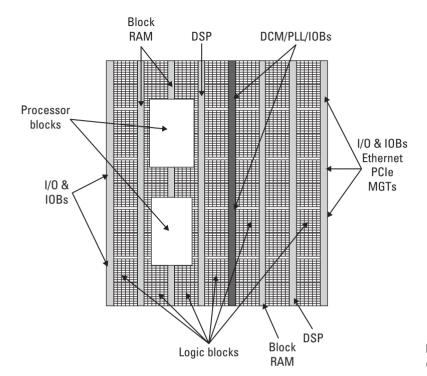

The role of FPGA devices has evolved over the years. Previously, the most common use of the technology was to replace a handful of individual small- and medium-scale IC devices, such as the ubiquitous 7400 series logic, with a single FPGA device. With well-known improvements and refinements in semiconductor technology, the number of transistors per IC chip has increased exponentially. This has been a boon for FPGA devices, which have increased dramatically in both programmable logic *capacity* and functional *capability*. By capacity, we are referring to the number of equivalent logic gates available; by capability we are referring to a variety of fixed, special-purpose blocks that have been introduced, both of which are discussed in more detail throughout this book.

As a result of this growth, modern FPGAs are able to support processors, buses, memory controllers, and network interfaces, as

Blank "slate" (when powered on)

After configuration

Figure 1.1. A 10,000-meter view of an FPGA; a blank slate that can be configured to implement digital circuits after the chip has been fabricated.

well as a continually increasing number of common peripherals, all on a single device. With the addition of a modern operating system, such as Linux, these FPGAs begin to appear more like a desktop PC in terms of functionality and capability, albeit on a single IC chip. Furthermore, with Open Source operating systems comes a plethora of Open Source software that can be leveraged by FPGA based designs.

We use the term *Platform FPGA* to describe an FPGA device that includes sufficient resources and functionality to host an entire system on a single device. The distinction is somewhat arbitrary, as there is no physical difference between a large FPGA device and a Platform FPGA device. Rather it is a matter of perspective: how the developer intends to use the device. We would say that an ordinary FPGA is generally used as a peripheral and plays a supporting role in a computing system. In contrast, a Platform FPGA has a central role in the computing system.

Overall, FPGAs offer a great deal to the embedded systems designer. Beyond simply reducing the numbers of chips, the Platform FPGA offers an enormous degree of flexibility. As it turns out, this flexibility is extremely valuable when designing systems to meet the complex and demanding requirements of embedded computing systems that are becoming so universal today. Often it is this flexibility that makes FPGA technology more appealing than traditional microprocessor-based solutions, Structured ASIC solutions, or other System-on-a-Chip (SoC) solutions.

Along with its advantages, FPGA technology also comes with a new set of challenges. Previously, one of the most important questions for an embedded systems designer was the choice of the processor. That choice usually dictated much of the remaining architecture (or at least limited the range of design choices). With Platform FPGAs, in order to fully utilize their capabilities and cost savings, a much wider pool of system developers needs to be able to combine computer engineering, programming, system analysis, and technical skills.

The aim of this book is to draw this necessary information together into a single text so as to provide the reader with a solid and complete foundation for building embedded systems on Platform FPGAs. This includes the underlying engineering science needed to make system-level decisions, as well as the practical skills needed to deploy an assembled hardware and software system.

The organization of this book reflects that twofold mission: each chapter consists of a set of white pages followed by a set of gray pages. The white pages emphasize the more theoretical concepts and slow-changing science. The gray pages provide descriptions of state-of-the-art technology and emphasize practical solutions to common problems.

The specific learning objectives of this chapter are straightforward.

- We begin with an abstract view of a computing machine and define an embedded system by distinguishing it from a generalpurpose computing system. Since we are using a Platform FPGA device to develop application-specific, custom computing machines, it is important to revisit the traditional concepts of hardware and software and, in particular, describe the two very different compute models used by each.

- Next, we consider some of the specific challenges that embedded systems designers face today. These include short product lifetimes leading to tight project development schedules, increased complexity, new requirements, and performance metrics that often define the degree of success. The complex interplay of these challenges presents one of the most important problems facing the next generation of embedded systems.

- The white pages of this chapter end with a section describing Platform FPGA characteristics and why these devices are well suited to meet these complex demands facing modern embedded systems designers today.

In the gray pages, a practical example using a fictitious scenario is presented; we briefly describe how to set up the software tools needed throughout the book and show to how to create the obligatory "Hello, World!" on a Platform FPGA development board. Overall, the goals of this chapter are to establish a solid motivation for using Platform FPGAs to build embedded systems and to initiate the reader on how to use the development tools.

# 1.1. Embedded Systems

In the simplest sense, an embedded system is a specialized computing machine. A *computing machine* (or just *computer*) is

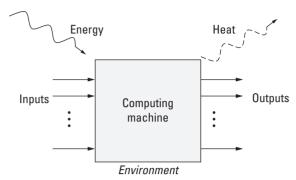

Figure 1.2. An abstract view of a computing system.

frequently modeled as a system that includes inputs, outputs, and a computation unit. The machine exists in some sort of *environment* that provides the energy to propel the machine. In addition to the manipulation of information, the computing machine produces heat that is returned to the environment. This organization is illustrated in Figure 1.2. (This very abstract figure is fleshed out in the next chapter.)

When the machine is being used, it is said to be executing and that period of time is called "run-time." When the machine is not executing, it is said to be "off-line." The inputs, which come from the environment, determine the outputs, which are conveyed from the machine to the environment. The inputs and outputs are often physical signals and as such are assigned meaning depending on the context of the problem, which is the point of building computing machines: to solve problems.

The personal computer (or desktop) is a well-known example of a computing machine but there are a multitude of others as well. The slide rule and the abacus are old-fashioned mechanical machines that were used to do arithmetic. These have since been replaced by the electronic calculator, which is an electronic computing machine.

# 1.1.1. Embedded and General-Purpose

Depending on how the computing machine is used, we classify it as either embedded or general-purpose. An *embedded computing system* (or simply an embedded system) is a computing machine that is generally a component of some larger product and its purpose is narrowly focused on supporting that product. In other words, it is a computing machine dedicated to a specific purpose. In terms of the abstract machine in Figure 1.2, the environment of an embedded computing system is the product it is part of. The

end user of the product typically does not directly interact with the embedded system, or interacts with only a limited interface, such as a remote control. Even though the computer may be capable of more, the embedded system is typically restricted to perform a limited role within the enclosing product, such as controlling the behavior of the product.

There are numerous examples of embedded systems. They are ubiquitous and have permeated most aspects of modern life: from the assortment of consumer electronics (DVD players, MP3 players, game consoles) we interact with almost daily, to energy-efficient refrigerators and hotel key-card activated door handles. Even large, heavy earth-moving equipment typically has hundreds of sensors and actuators connected to one or more embedded systems.

In contrast, a general-purpose computing system is a product itself and, as such, the end user directly interacts with it. Another way to put it, the end user explicitly knows the product they are buying is a computer. General-purpose systems are characterized by having relatively few, standardized inputs and outputs. These include peripherals, such as keyboards, mice, network connections, video monitors, and printers. Embedded systems often have some of these standard peripherals as well, but also include much more specialized ones. For example, an embedded system might receive data from a wide range of special-purpose sensors (accelerometers, temperature probes, magnetometers, push button contact switches, and more). It may signal output in a variety of ways (lamps and LEDs, actuators, TTL electrical signals, LCD displays, and so on). These types of inputs and outputs are not typically found in general-purpose computers. Furthermore, how the inputs and outputs are encoded may be device specific in an embedded system. In contrast, general-purpose computers use standard encodings. For example, the movement of a mouse is typically transmitted using low-speed serial communication and many manufacturers' mice are interchangeable. Another example is each key on a keyboard has fixed standard ASCII encoding. While an embedded system may also use these standards, it is just as likely that it will receive its input encoded in the form of a pulse frequency. Both may look similar electrically but how meaning is attached to the signals is very different.

Ultimately, such a precise definition of an embedded system can be difficult to agree with depending on what an individual considers a "larger product." For example, is a handheld computer an embedded system? If so, what is its enclosing product? It is not used to control anything. Furthermore, the computing system is exposed to the user: the user can download

general-purpose applications. So by the criterion just described, it is not an embedded system. A handheld computer shares many characteristics of embedded systems. (For example, like an embedded system, handhelds are very sensitive to size, weight, and power constraints.) For this reason some might be inclined to call it an embedded system. Now add a mobile phone application to the system and most would agree that this is an embedded system. With the addition of some specialized inputs and outputs, a general-purpose system can be viewed as an embedded system. So, the exact boundary between general-purpose and embedded is not black and white but rather a spectrum.

General-purpose systems strive to strike a balance, compromising performance in some areas in order to perform well over a broad range of tasks. More to the point, general-purpose computers are engineered to make the common case fast. Since embedded systems commonly have a more narrowly defined purpose, designers have the benefit of more precise domain information. This information can be used during the product development to improve performance. Often, this can lead to very substantial improvements.

For example, a general-purpose computer may be used to process 50,000 frames of video from a home camcorder and then later the same computer may need to handle spreadsheet calculations while serving World Wide Web content. For a single user, this computer has to handle these functions (and many others) reasonably well. As long as other issues, such as energy use, are reasonable, the user is happy. However, an embedded system designer might know that their system will never need to do spreadsheet calculations and the engineer can exploit this knowledge to better utilize the available resources.

Most computer courses target general-purpose computing systems. Operating systems, programming languages, and computer architecture are all taught with general-purpose computing machines in mind. That is appropriate because — embedded or not — many of the principles are the same. However, given the enormous presence of embedded computing systems in our day-to-day lives, it is worthwhile to accentuate the unique characteristics of embedded systems and focus a program of study on those.

# 1.1.2. Hardware, Software, and FPGAs

One of the differences between general-purpose computing and embedded computing is that embedded systems often require special-purpose hardware and software. It is worthwhile to define these terms before we proceed. Furthermore, Platform FPGAs begin to blur the distinction between hardware and software. Before we get into the details of FPGA technology, though, let's revisit the definitions of hardware and software.

Hardware refers to the physical implementation of a computing machine. This is usually a collection of electronic circuits and perhaps some mechanical components. Simply put, it is made of matter and is tangible. For example, consider a computing machine implemented as a combinational circuit of logic gates (AND, OR, NOT) and assembled on a breadboard. The hardware is visible and the design physically occupies space. Another characteristic of hardware is that all of the components are active concurrently. When inputs are varied, changes in the circuit propagate through the machine in a predictable but not necessarily synchronized manner.

Software, however, is information and as such does not manifest itself in the physical world. *Software* is a specification that describes the behavior of the machine. It is generally written in a programming language (such as C, MATLAB, or Java) and this representation of desired machine behavior is called a *program*. While it is possible to print a program on paper, it is a representation of the program that exists in the physical world. The software is information expressed on the printout and is inherently intangible. (Note that a person who is composing software is called a *programmer* and that the act is called *programming*.)

These traditional definitions of hardware and software have served us well over the years, but with the advent of FPGAs and other programmable logic devices in general, these definitions and the distinction of what is hardware and what is software become less clear.

# 1.1.3. Execution Models

One of the most challenging aspects of embedded systems design is the fact that one has both hardware and software components in the design. These have fundamentally different execution models, which are highlighted.

Several programming paradigms exist for High-Level Languages (functional, object-oriented, etc.). However, at the machine level, all commercial processors use an imperative, fetch-execute model with an addressable memory. In software, this sequential execution model serializes the operations, eliminating any explicit parallelism. As a result, operations are completed in order, alleviating the software programmer from the arduous task of synchronizing the execution of the program. In contrast, hardware is naturally parallel and computer engineers must explicitly include synchronization in their design. This concept of

sequential, implicitly ordered operations versus the unrestricted compute model is especially important in FPGA designs and is a topic that we will continue to address throughout this book.

A subtle point is that it is commonplace to refer to some components of our Platform FPGA system as "hardware" when, in fact, these components are written like software. That is, the component is a specification of how the device is to be configured. The real, physical hardware is the FPGA device itself. Thus, in place of the conventional definition of hardware given earlier, we will distinguish hardware and software components of our system based on their model of execution. Earlier we said that software is characterized by a sequential execution model and that the hardware execution model is distinctly nonsequential. In other words, software will refer to specifications intended to be executed by a processor, whereas hardware will refer to specifications intended to be executed on the fabric of an FPGA and, on occasion, in a broader sense, the physical components of the computing system. To make this important distinction more concrete, consider the following computation:

$$R0+R1+R2 \rightarrow Acc$$

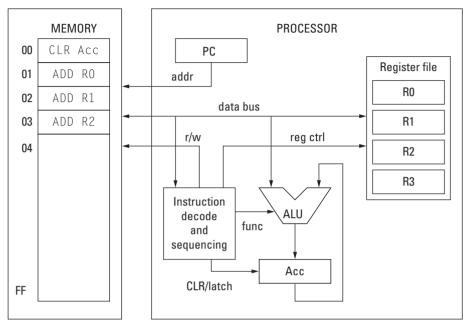

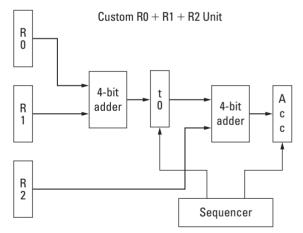

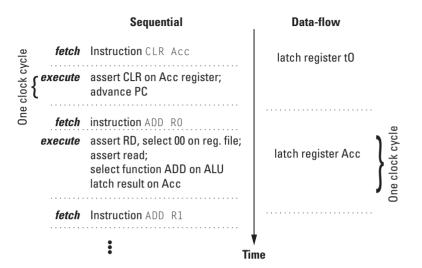

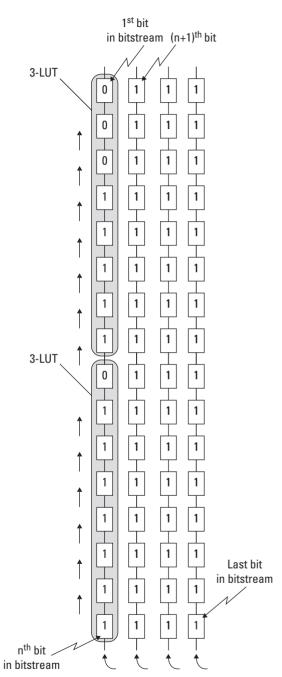

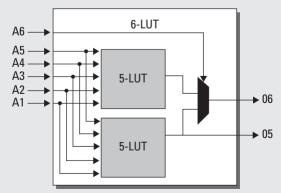

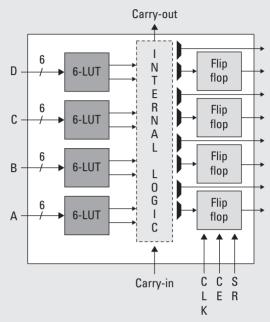

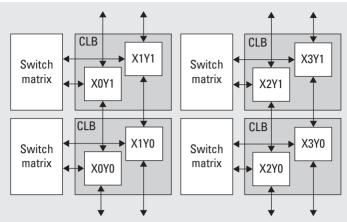

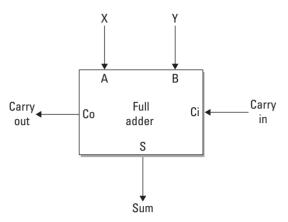

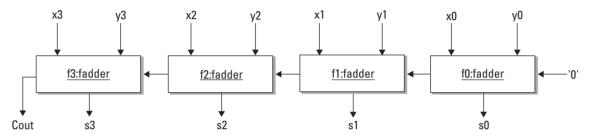

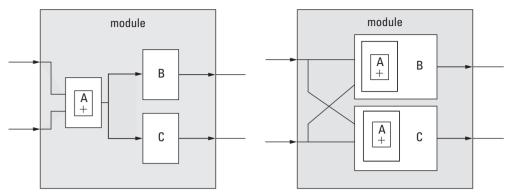

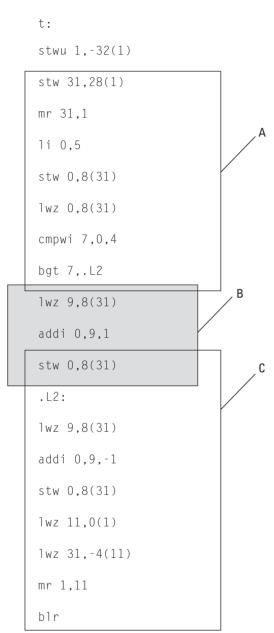

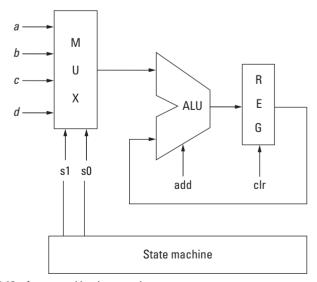

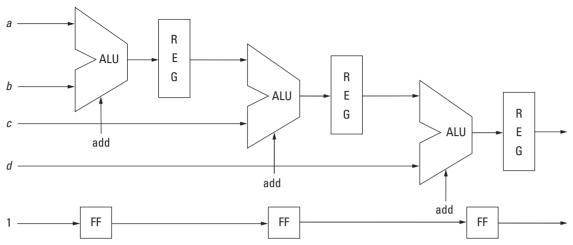

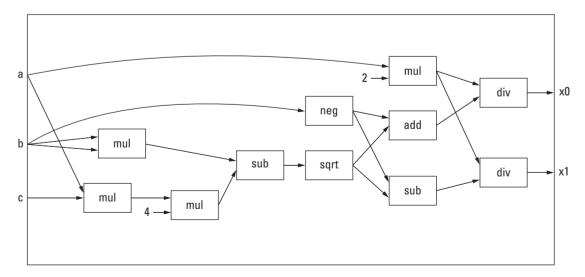

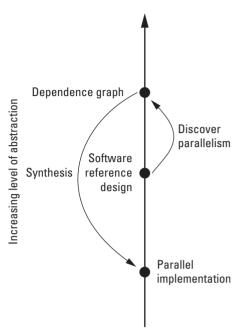

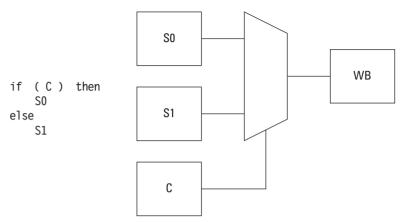

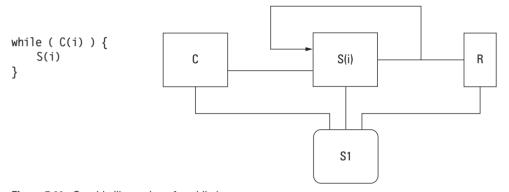

Assume that all four names are registers. The computation implemented in the sequential model is illustrated in Figure 1.3. It shows the traditional fetch-execute machine. The dashed box highlights on the main mechanism. The ALU circuit is time-multiplexed to perform each addition sequentially. A substantial part of the circuit is used to decode and control the time steps. This is commonly referred to as the von Neumann stored-program compute model. We will continue to refer to it as the sequential execution model. In contrast, a nonsequential execution model can take a wide variety of forms, but is clearly distinguished from sequential execution by the absence of a general-purpose controller that sequences operations and the explicit time-multiplexing of named, fixed circuits. A nonsequential execution implementation of this computation is illustrated in Figure 1.4. This is generally known as a data-flow model of execution, as it is the direct implementation of a dataflow graph. (We use the broader sense of the term throughout this book; the data-flow architectures studied in the 1980s and 1990s incorporate more detail than this.)

In terms of how these two computing models work, consider their operation over time. In Figure 1.5, time advances from top to bottom. Each "slot" delineated by the dotted lines indicates what happens during one clock cycle. It is important to note that the speed of the two computing models cannot be compared by counting the number of cycles — the clock frequencies for each

Figure 1.3. A sequential model.

Figure 1.4. A nonsequential model.

are different. A typical FPGA clock period might be  $5\times$  to  $10\times$  longer than a processor implemented in the same technology. Also, modern processors typically operate on multiple instructions simultaneously, which has become crucial to their performance.

With this understanding, we can say that software runs on a processor where a *processor* is hardware that implements the

**Figure 1.5.** A cycle-by-cycle operation of sequential and data-flow models.

sequential execution model. Note that the terms Central Processing Unit (CPU) and microprocessor are common synonyms for processor. Hardware will be the specification that we use to configure the FPGA and does not use the sequential execution model.

# 1.2. Design Challenges

Now that we have a better understanding of what an embedded system is, it is worthwhile to understand a little bit about how embedded systems projects work. This section discusses the life cycle of a typical project, describes typical measures of embedded system success, and closes with a summary of costs.

# 1.2.1. Design Life Cycle

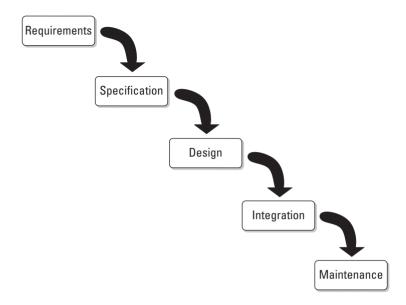

There are many books on how to manage an engineering project. Our goal in this section is simply to highlight a couple of terms and describe the design life cycle of a project to provide context for remaining sections. This life cycle, illustrated in Figure 1.6, is sometimes referred to as the "waterfall model." It is meant to suggest that going upstream (i.e., returning to a previous stage because of a bug or mistake in the design) is considerably more challenging than going downstream.

Whether initiated by a marketing department or by the end user, the first stage is called *requirements*. As the name suggests, the step is to figure out what the product is required to do. Often this will start as a very broad, abstract statement, and it is the developer's job to establish a concrete list of user measurable

Figure 1.6. A"waterfall model" description of a project life cycle.

capabilities that, if met, the end user would agree the project was a success.

The next stage in is called *specifications*. In contrast to requirements, specifications are usually written for the developer, not the end user. Created from the requirements, they are used to judge whether a particular piece of code or hardware is correct. Often a specification comes from a particular requirement, but some specifications may result as the combination of several requirements or as the result of preplanning the design of the product. It is reasonable to develop a set of metrics at this stage that define the correct behavior (in terms of implementation).

The *design* stage follows next. Usually a developer is contemplating a working design throughout all of the previous stages; this is where the design is formalized. Formats, division of functionality into modules, and algorithm selection are all part of this stage. There are numerous methodologies for how to design software and some include developing a prototype, whereas others call for reiterating over specifications and requirements. Others espouse coding a solution as fast as possible under the adage that "get your first design finished as soon as possible because you always throw out the first one." For FPGA designs, a developer is typically designing the physical components, electrical and mechanical, at this stage as well.

The fourth stage — called *integration* (or in some methodologies, "testing") — begins when the physical components become available. All of the components are combined, and the

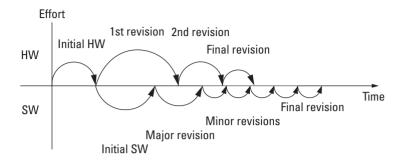

**Figure 1.7.** Rate of revisions in developing hardware and software.

functionality tests developed during the specification stage are applied. For custom Printed Circuit Boards (PCBs), there is usually an incremental process of (1) testing the electrical connectivity, (2) applying low-voltage power and verifying the digital components, (3) testing the high-voltage components (if any), and then finally loading the software. The process is called "bringing up a board," and the idea is to minimize potential damage due to any mistakes in the design or fabrication process. By testing incrementally, it also helps locate the mistakes that inevitably will exists.

After integration, the product is generally ready to be delivered (if it is a one-off custom design) or manufactured in mass. The final stage, *maintenance*, begins once the product has left integration. As the name suggests, it deals with fixing problems that were discovered after the product begins to ship. For FPGA-based designs, there is much that can be done in this stage because, after all, the device is programmable in the field! More to come on that later.

An alternative view of the design and integration stages is shown in Figure 1.7. The point of this illustration is to show the hardware (top) and software (bottom) revisions of the designs. Often, before software development can begin, some initial design effort is needed to produce the first hardware (first silicon). This can also be the time waiting for a development board to be fabricated. Once the hardware arrives, the software development can swing into full gear. Each arc represents another revision, where the large area under the arc indicates a major revision and smaller arcs represent minor revisions. A project may only have so much time to revise hardware, so the relatively few major revisions are shown. Software may be able to make many small revisions, especially toward the end of the design process.

## 1.2.2. Measures of Success

For the last several decades in the general-purpose computer world, the top design consideration has been speed (rate of execution). Computing machines were compared based on how fast they completed a task. In the embedded systems world, success is a combination of *requirements* and *performance metrics*. The requirements are capabilities that the system must meet to be functionally correct. Metrics are measured on a continuum. Also, an embedded systems design is, by definition, constrained by its environment (i.e., the larger product it is part of). This necessarily means that success is a multifaceted measure.

Clearly, the requirements and specifications guide the design of an embedded system. The requirements will define capabilities that must be met. Often there exist additional criteria (which may or may not be explicitly provided) that help judge the success of the product. We call these extra criteria performance metrics. Metrics are generally measured on a scale, such as "faster is better" or "lighter is better." For example, a six-week battery life might be a requirement but a product may also be judged by its battery life metric. A product that typically runs for eight weeks between charges is generally considered better than one that simply meets its six-week requirement.

Of course, a developer does not want to blindly "over engineer" a product because there are real costs associated with many decisions. In order to make sensible decisions given a fixed amount of resources, a developer needs quantifiable metrics as a guide. There are a number of quantifiable metrics that embedded systems developers may use; three common metrics are considered here: speed, energy, and packaging.

#### Speed

Throughout most computer-related undergraduate curricula, the idea of speed is theoretical. That is to say an algorithm is evaluated in terms of the number of time steps it takes to complete. Usually this is written in terms of the size of its input, n. This is a very effective tool for comparing the relative merits of algorithms, but for embedded systems, it is not as useful. Embedded systems, for example, typically run until the power is turned off — so picking a fixed n as an input is often impossible! Instead, it is more useful to measure the speed of the individual components.

If the computing machine has a dedicated purpose, then the speed may be characterized as a *minimum speed* requirement. In this case, the speed can be thought of as a "cliff" function: if you are heading toward a cliff, being able to stop in time is sufficient but not stopping in time has dramatic consequences. For many dedicated systems, there are limited benefits in exceeding the target speed, but falling short of the target does not gradually degrade the performance of the system.

For scientific applications, the speed — that is, the rate of computation — is usually the metric that trumps all others. Heat and packaging are important; however, as long as the machine can be physically built and the heat generated by the machine removed is at a reasonable cost, then the key factor that distinguishes one system from another is how fast it completes a given task. Likewise, for many business applications, reducing the amount of time that an end user spends waiting for a result provides a competitive edge over another machine. This is sometimes characterized as "how fast the time piece goes away" in reference to a mouse pointer icon that indicates the machine is working. In these and other general-purpose cases, performance increases as the speed of the machine increases. For such systems, an *unbounded speed* requirement means that faster is better.

Unlike many general-purpose systems, embedded systems incorporate both speed requirements. When the computing machine is used for controlling the product and the speed is not directly observable by the end user, then there is usually just a minimum speed requirement. The machine just has to be "fast enough" in order for the product to function correctly. If the end user can observe the speed, then an unbounded speed requirement may be in effect. For example, suppose the task is to skip forward to the next song in the playlist. An unbounded speed requirement is reasonable here because if the target is two seconds, then exceeding this results in a better end-user experience. Faster response times can translate into a measurable advantage. If the embedded system is designed to increase the energy efficiency of a household appliance, then exceeding the minimum speed actually degrades the overall performance (because a faster system presumably consumes more energy).

Speed requirements are usually specified for each use case. This often results in multiple tasks that, to some extent, share resources in the system. Operating systems can be used to manage those shared resources by creating a virtual environment for each task and then time-multiplexing the tasks. Ordinary operating systems schedule these tasks in real time with an assumption that the tasks have unbounded speed requirements. However, embedded system applications often need a mechanism to relate tasks' progress in their individual virtual times to the events in real time. An operating system that provides these mechanisms is called a real-time operating system.

Scheduling in real-time operating systems is challenging because, for a variety of reasons, the amount of time a particular task is going to take is not always known. Hence, before we leave the speed component of performance, it is worthwhile to note that *predictability* is valuable. Predictability can improve the scheduler of a real-time operating system, which allows us to more carefully specify minimum speed requirements.

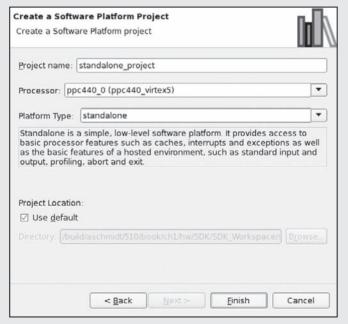

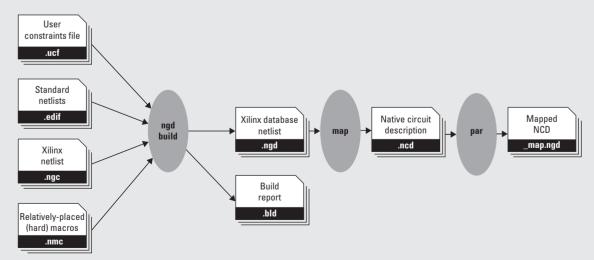

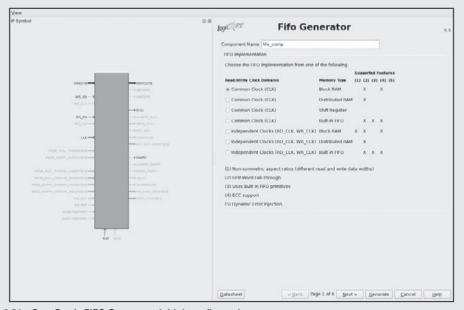

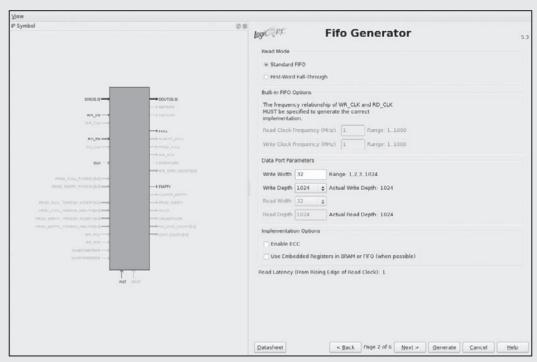

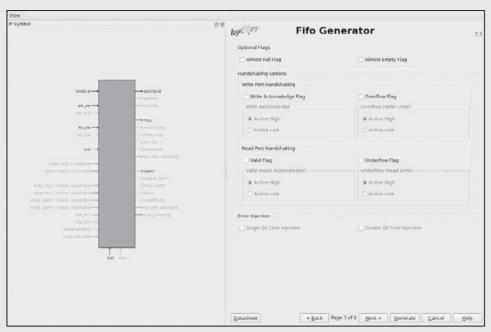

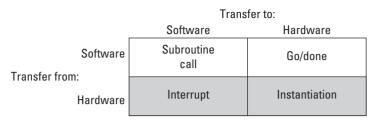

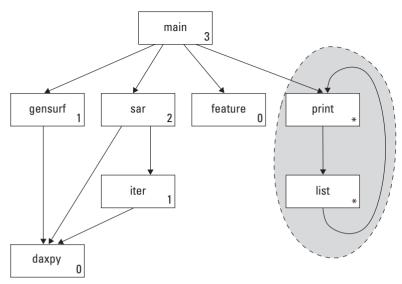

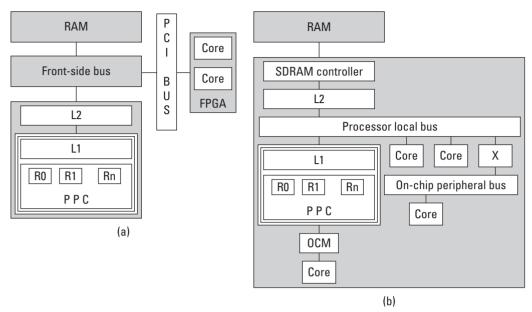

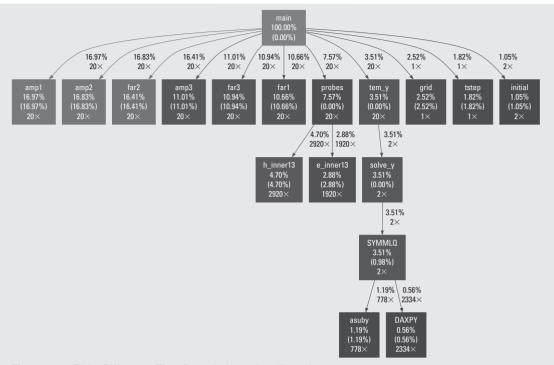

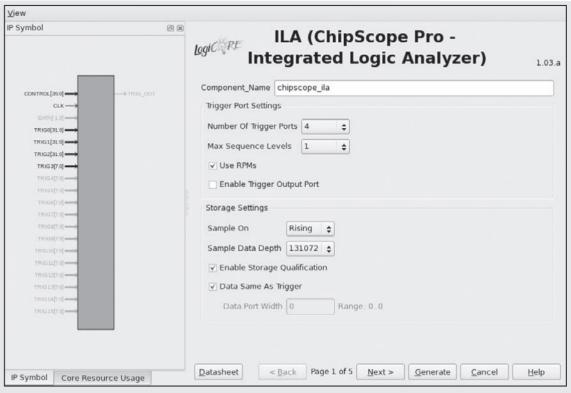

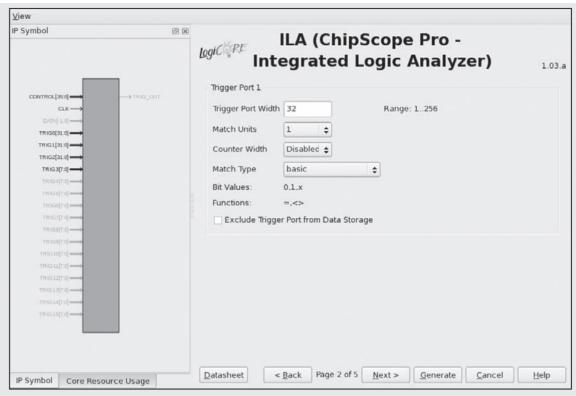

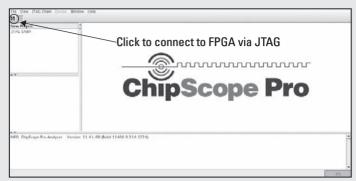

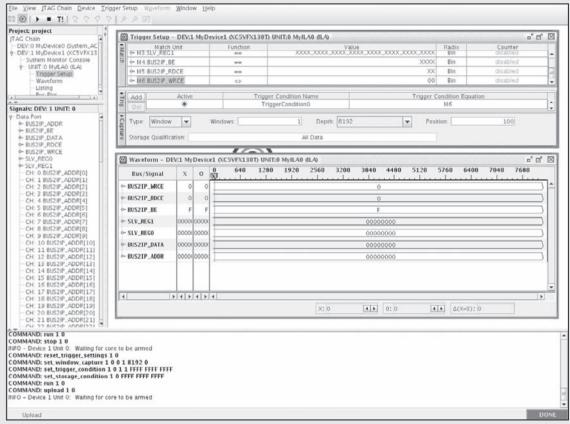

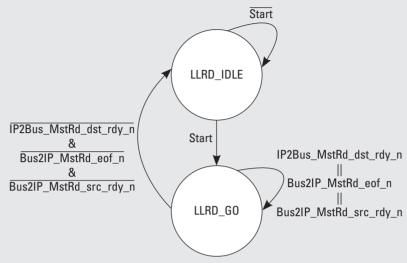

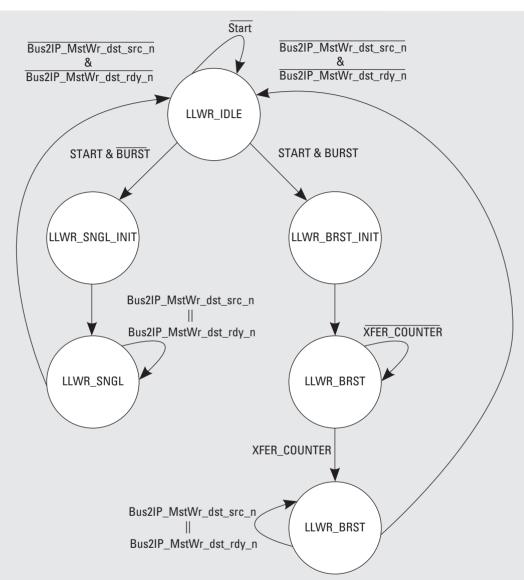

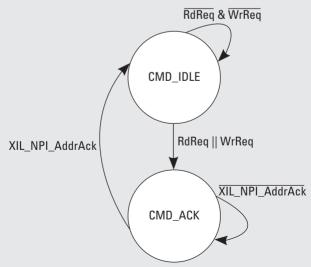

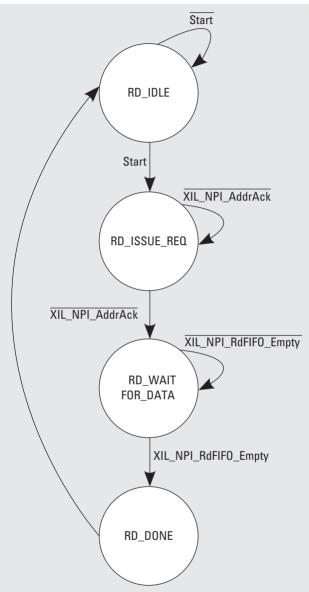

#### Energy and Power