# Contents

| $P_I$ | eface i                  | to the fourth edition                                     | XI  |  |  |

|-------|--------------------------|-----------------------------------------------------------|-----|--|--|

| A     | knowl                    | edgments                                                  | xii |  |  |

| 1     | Number systems and codes |                                                           |     |  |  |

| 8     | 1.1                      | Introduction                                              | 1   |  |  |

|       | 1.2                      | Number systems                                            |     |  |  |

|       | 1.3                      | Conversion between number systems                         | 2   |  |  |

|       | 1.4                      | Binary addition and subtraction                           | 5   |  |  |

|       | 1.5                      | Signed arithmetic                                         |     |  |  |

|       | 1.6                      | Complement arithmetic                                     | 7   |  |  |

|       | 1.7                      | Complement representation for binary numbers              | 7   |  |  |

|       | 1.8                      | The validity of 1's and 2's complement arithmetic         | 9   |  |  |

|       | 1.9                      | Offset binary representation                              | 10  |  |  |

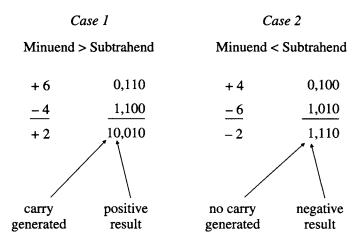

|       | 1.10                     | Addition and subtraction of 2's complement numbers        | 10  |  |  |

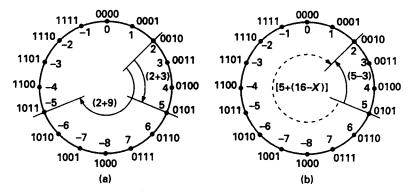

|       | 1.11                     | Graphical interpretation of 2's complement representation | 12  |  |  |

|       | 1.12                     | Addition and subtraction of 1's complement numbers        | 13  |  |  |

|       | 1.13                     | Multiplication of unsigned binary numbers                 | 13  |  |  |

|       | 1.14                     | Multiplication of signed binary numbers                   | 14  |  |  |

|       | 1.15                     | Binary division                                           | 15  |  |  |

|       | 1.16                     | Floating point arithmetic                                 | 16  |  |  |

|       | 1.17                     | Binary codes for decimal digits                           | 18  |  |  |

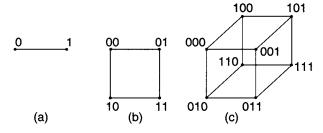

|       | 1.18                     | n-cubes and distance                                      | 19  |  |  |

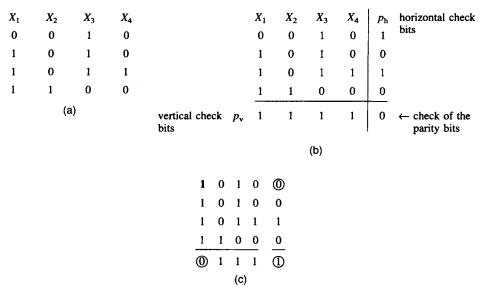

|       | 1.19                     | Error detection and correction                            | 20  |  |  |

|       | 1.20                     | The Hamming code                                          | 21  |  |  |

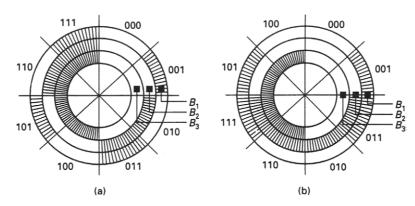

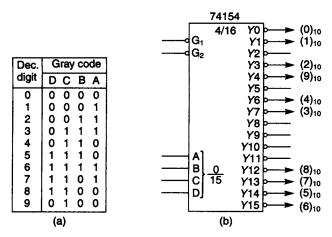

|       | 1.21                     | Gray code                                                 | 23  |  |  |

|       | 1.22                     | The ASCII code                                            | 24  |  |  |

| 2     | Boole                    | ean algebra                                               | 28  |  |  |

|       | 2.1                      | Introduction                                              | 28  |  |  |

|       | 2.2                      | Boolean algebra                                           | 28  |  |  |

|       | 2.3                      | Derived Boolean operations                                | 29  |  |  |

|       | 2.4                      | Boolean functions                                         | 29  |  |  |

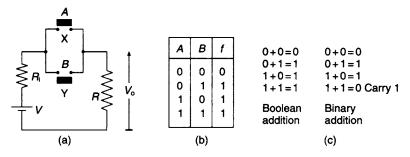

|       | 2.5                      | Truth tables                                              | 30  |  |  |

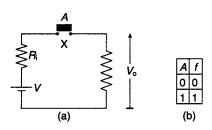

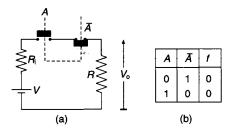

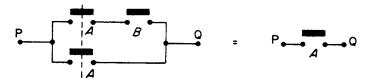

|       | 2.6                      | The logic of a switch                                     | 30  |  |  |

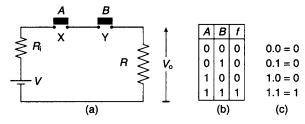

|       | 2.7                      | The switch implementation of the AND function             | 31  |  |  |

|       | 2.8                      | The switch implementation of the OR function              | 32  |  |  |

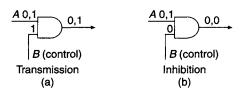

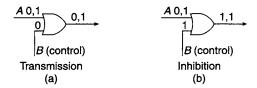

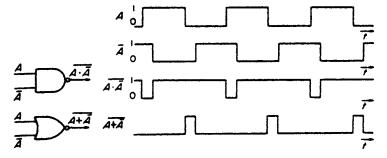

|       | 2.9                      | The gating function of the AND and OR gates               | 33  |  |  |

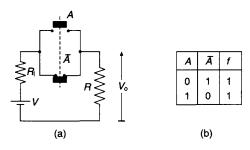

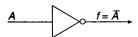

|       | 2.10                     | The inversion function                                    | 33  |  |  |

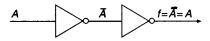

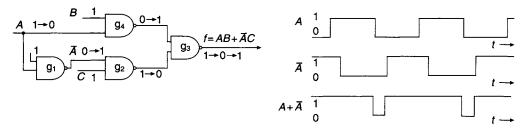

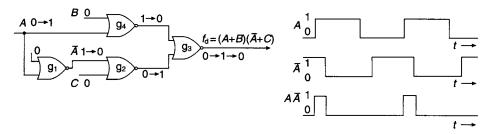

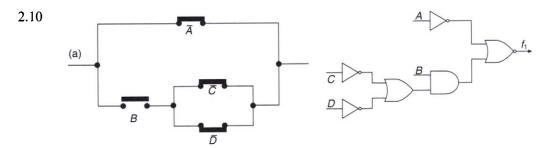

|       | 2.11                     | Gate or switch implementation of a Boolean function       | 34  |  |  |

|       | 2.12                     | The Boolean theorems                                      | 34  |  |  |

|   | 2.12 | Consideration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20 |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

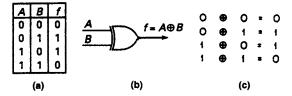

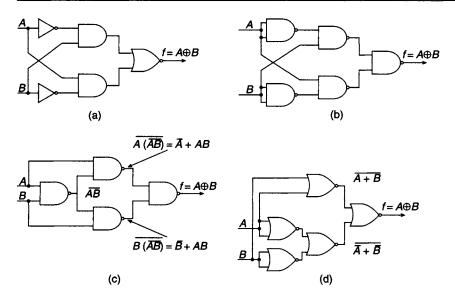

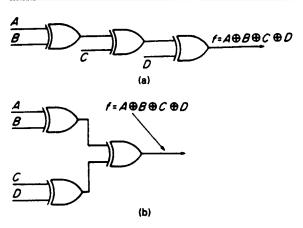

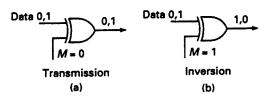

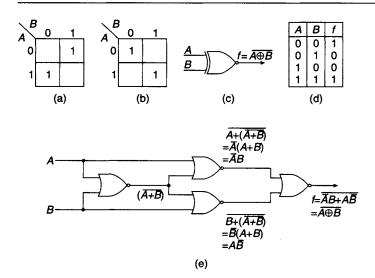

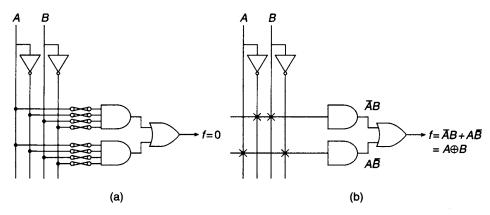

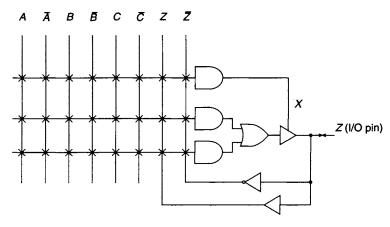

|   | 2.13 | Complete sets The analysis OR (VOR) function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 38 |

|   | 2.14 | 8. TO STATE (TO STATE TO STATE STATE OF | 38 |

|   | 2.15 | The Reed–Muller equation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40 |

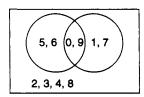

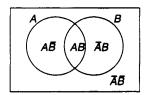

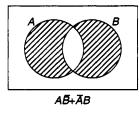

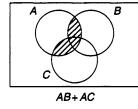

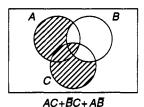

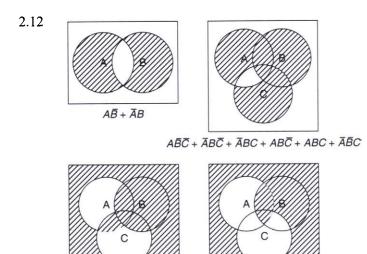

|   | 2.10 | Set theory and the Venn diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40 |

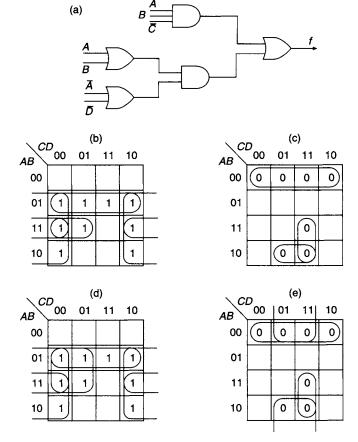

| 3 | Karn | augh maps and function simplification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 43 |

|   | 3.1  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 43 |

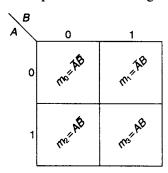

|   | 3.2  | Minterms and maxterms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 43 |

|   | 3.3  | Canonical forms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 44 |

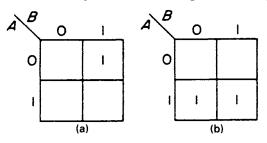

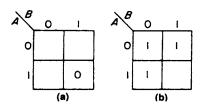

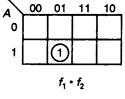

|   | 3.4  | Boolean functions of two variables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45 |

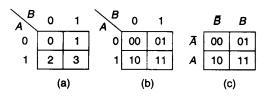

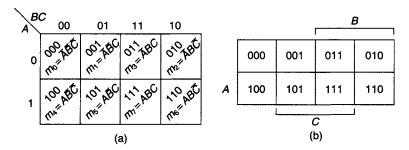

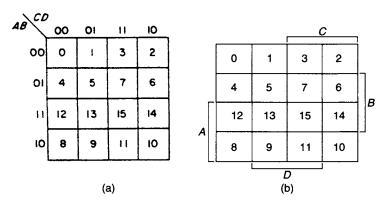

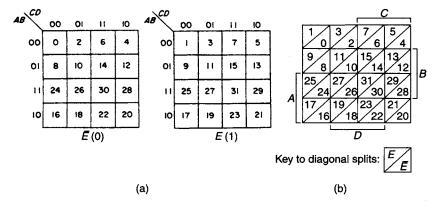

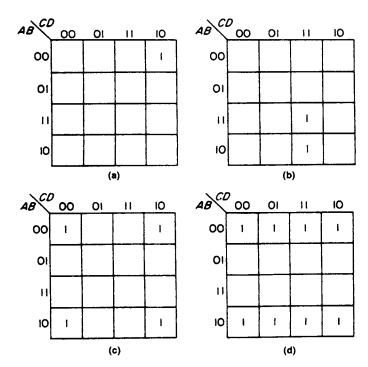

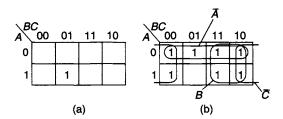

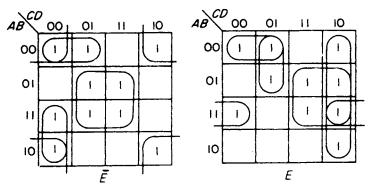

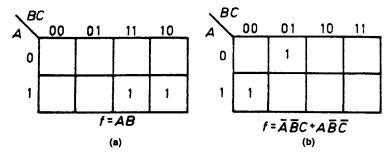

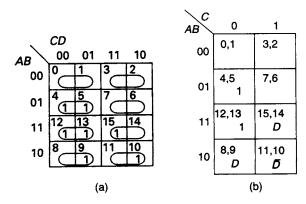

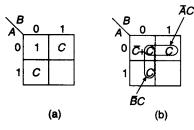

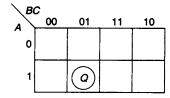

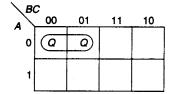

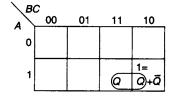

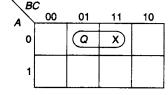

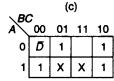

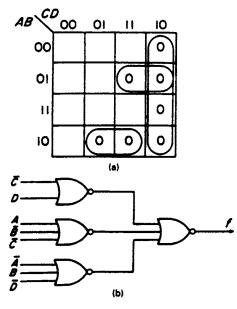

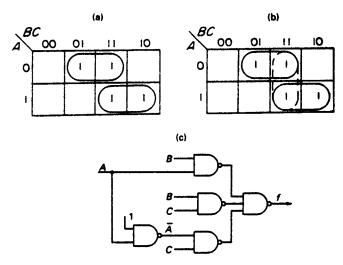

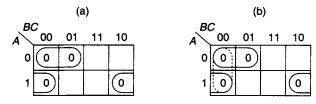

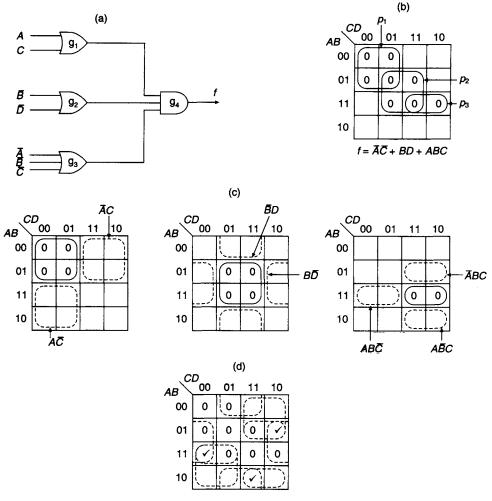

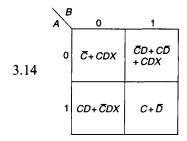

|   | 3.5  | The Karnaugh map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 46 |

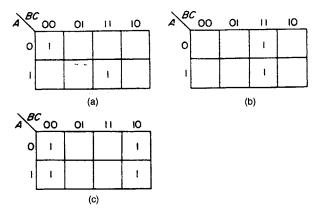

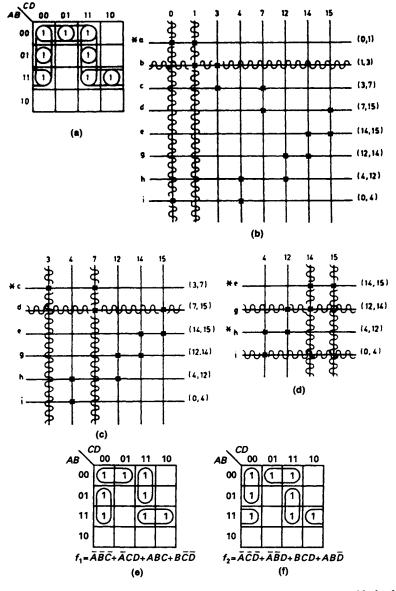

|   | 3.6  | Plotting Boolean functions on a Karnaugh map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 49 |

|   | 3.7  | Maxterms on the Karnaugh map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 50 |

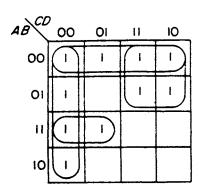

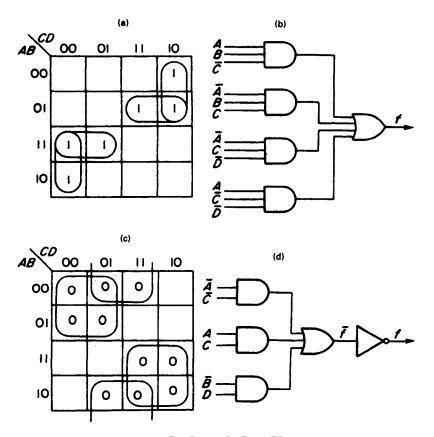

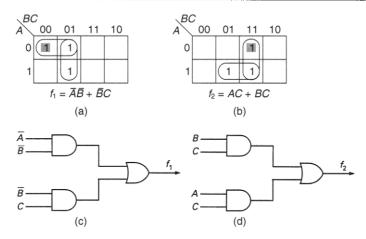

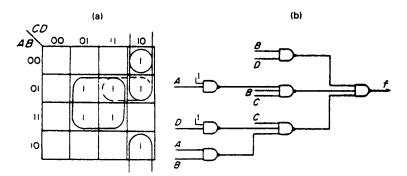

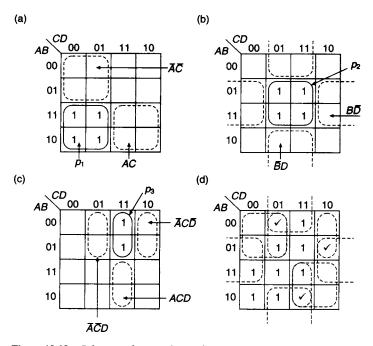

|   | 3.8  | Simplification of Boolean functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 51 |

|   | 3.9  | The inverse function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54 |

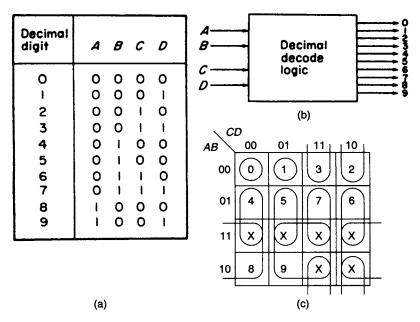

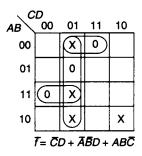

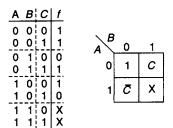

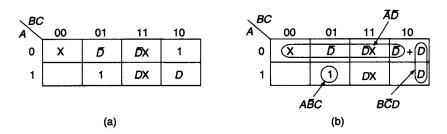

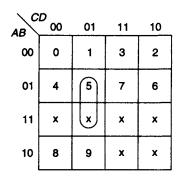

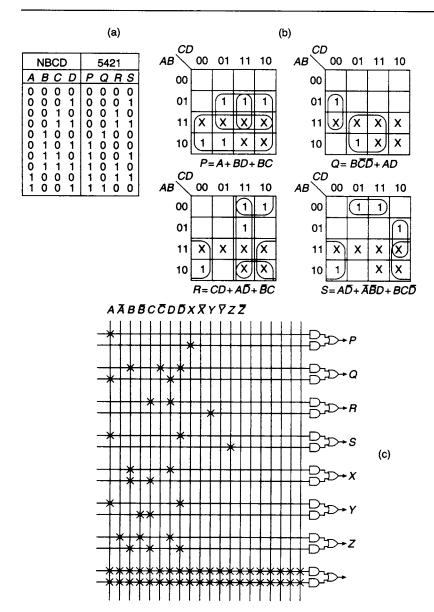

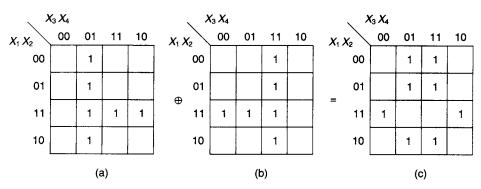

|   | 3.10 | 'Don't care' terms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55 |

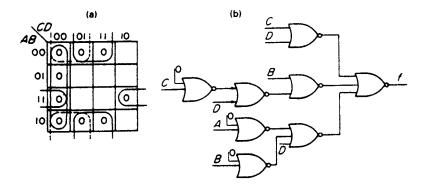

|   | 3.11 | Simplification of products of maxterms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57 |

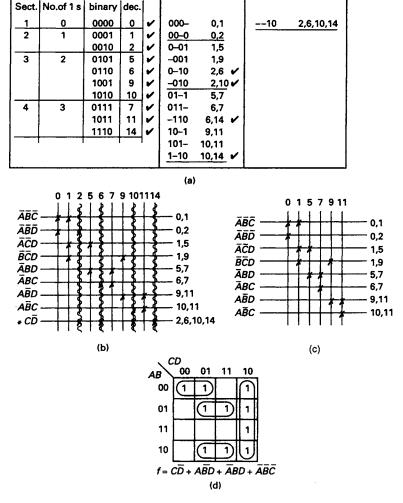

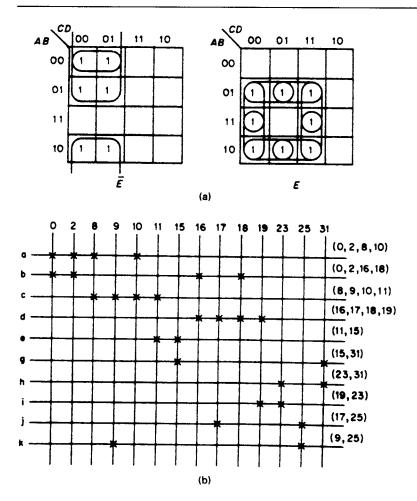

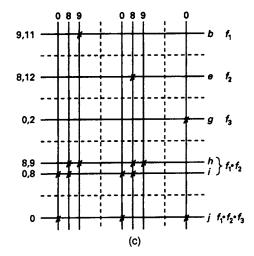

|   | 3.12 | The Quine-McCluskey tabular simplification method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 58 |

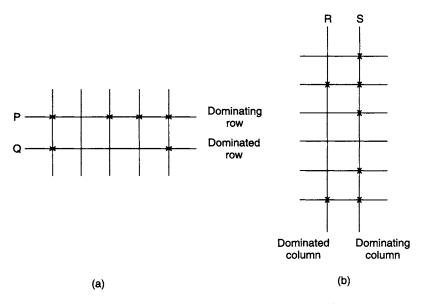

|   | 3.13 | Properties of prime implicant tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61 |

|   | 3.14 | Cyclic prime implicant tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61 |

|   | 3.15 | Semi-cyclic prime implicant tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 63 |

|   | 3.16 | Quine-McCluskey simplification of functions containing 'don't care' terms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64 |

|   | 3.17 | Decimal approach to Quine-McCluskey simplification of Boolean functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65 |

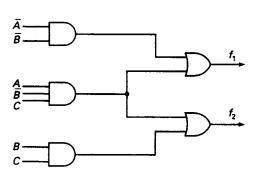

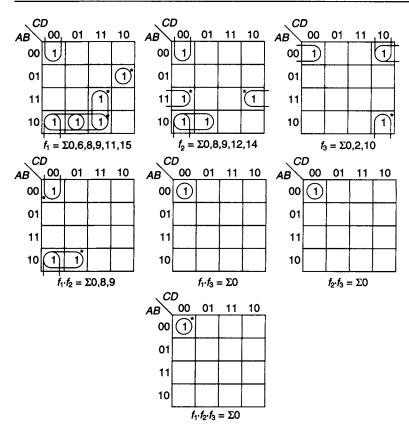

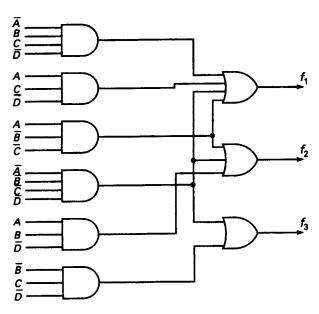

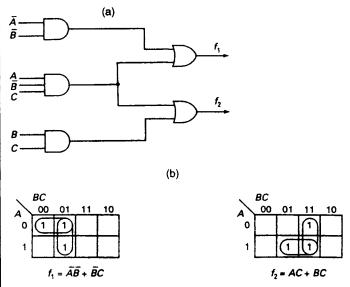

|   | 3.18 | Multiple output circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 67 |

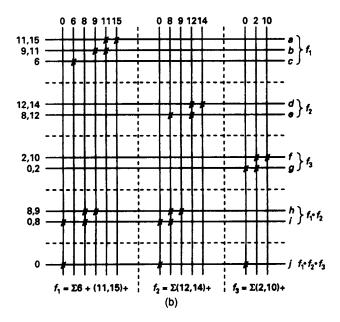

|   | 3.19 | Tabular methods for multiple output functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 70 |

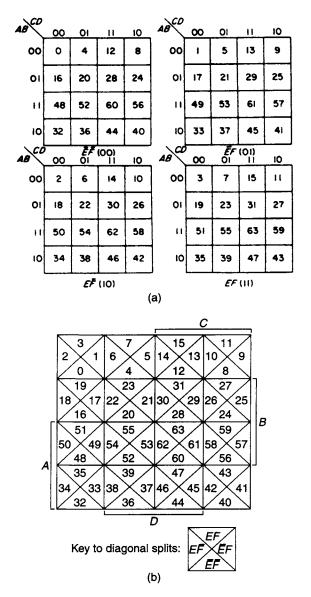

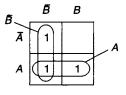

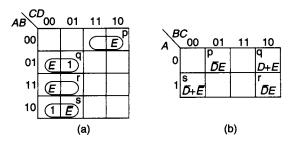

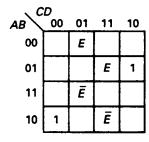

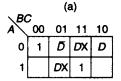

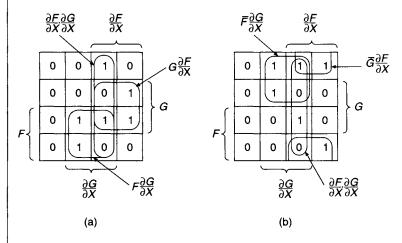

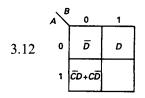

|   | 3.20 | Reduced dimension maps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 73 |

|   | 3.21 | Plotting RDMs from truth tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75 |

|   | 3.22 | Reading RDM functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 76 |

|   | 3.23 | Looping rules for RDMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 76 |

|   | 3.24 | Criteria for minimisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 77 |

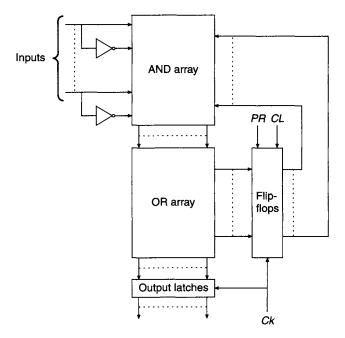

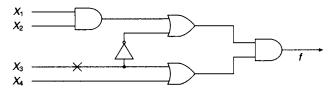

| 4 | Coml | binational logic design principles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 81 |

| Ö | 4.1  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 81 |

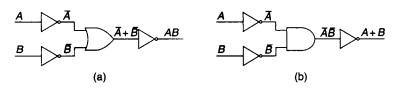

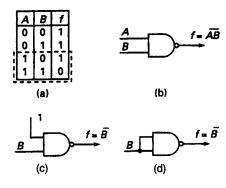

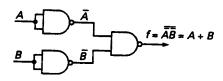

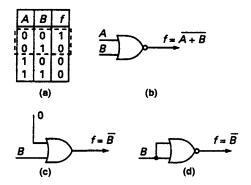

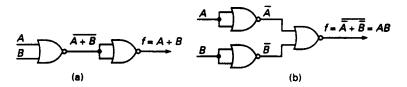

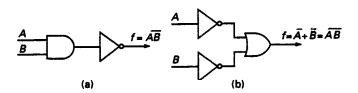

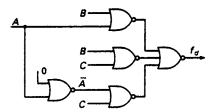

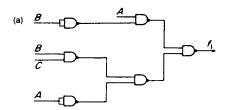

|   | 4.2  | The NAND function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 81 |

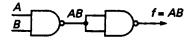

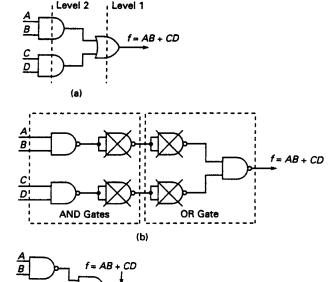

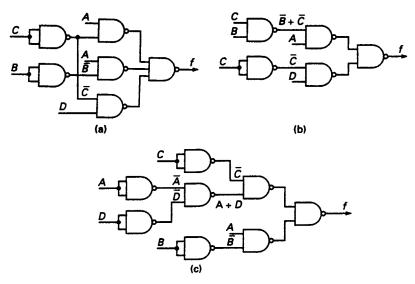

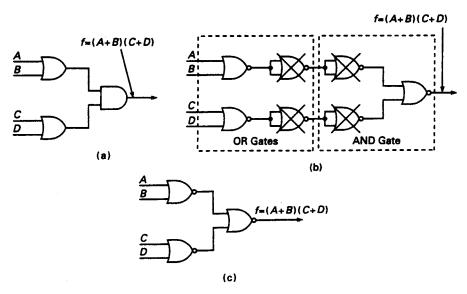

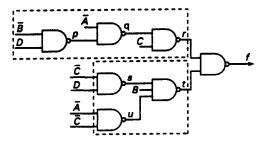

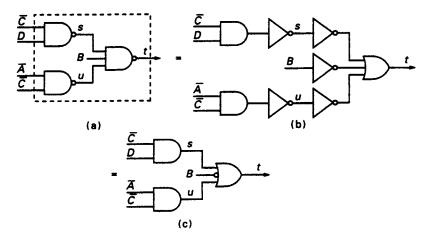

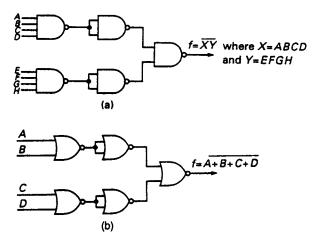

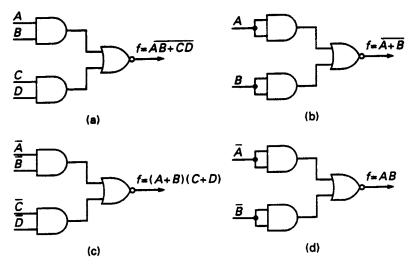

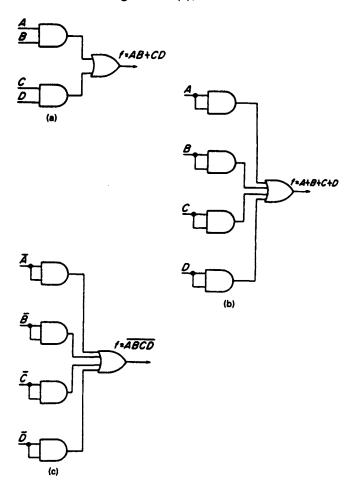

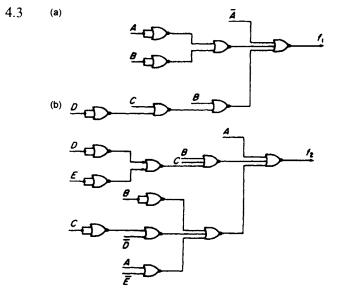

|   | 4.3  | NAND logic implementation of AND and OR functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 82 |

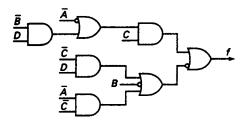

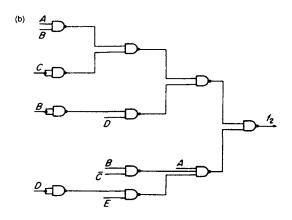

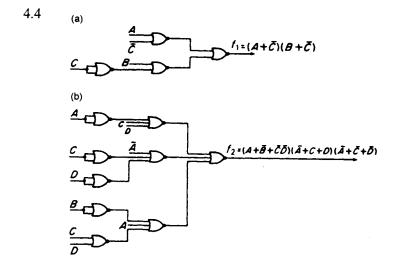

|   | 4.4  | NAND logic implementation of sums-of-products                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 83 |

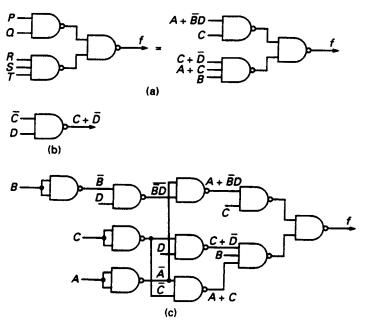

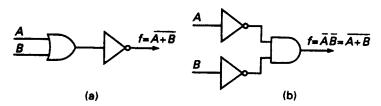

|   | 4.5  | The NOR function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 85 |