# Computer Architecture

Gérard Blanchet Bertrand Dupouy

First published 2013 in Great Britain and the United States by ISTE Ltd and John Wiley & Sons, Inc.

Apart from any fair dealing for the purposes of research or private study, or criticism or review, as permitted under the Copyright, Designs and Patents Act 1988, this publication may only be reproduced, stored or transmitted, in any form or by any means, with the prior permission in writing of the publishers, or in the case of reprographic reproduction in accordance with the terms and licenses issued by the CLA. Enquiries concerning reproduction outside these terms should be sent to the publishers at the undermentioned address:

ISTE Ltd 27-37 St George's Road London SW19 4EU UK

John Wiley & Sons, Inc. 111 River Street Hoboken, NJ 07030

USA

www.wiley.com

#### © ISTE Ltd 2013

www.iste.co.uk

The rights of Gérard Blanchet and Bertrand Dupouy to be identified as the author of this work have been asserted by them in accordance with the Copyright, Designs and Patents Act 1988.

Library of Congress Control Number: 2012951898

British Library Cataloguing-in-Publication Data A CIP record for this book is available from the British Library ISBN: 978-1-84821-429-3

Printed and bound in Great Britain by CPI Group (UK) Ltd., Croydon, Surrey CR0 4YY

# Table of Contents

| Preface                                        | xiii |

|------------------------------------------------|------|

| PART 1. ELEMENTS OF A BASIC ARCHITECTURE       | 1    |

| Chapter 1. Introduction                        | 3    |

| 1.1. Historical background                     | 3    |

| 1.1.1. Automations and mechanical calculators  | 3    |

| 1.1.2. From external program to stored program | 6    |

| 1.1.3. The different generations               | 8    |

| 1.2. Introduction to internal operation        | 13   |

| 1.2.1. Communicating with the machine          | 13   |

| 1.2.2. Carrying out the instructions           | 14   |

| 1.3. Future prospects                          | 15   |

| Chapter 2. The Basic Modules                   | 17   |

| 2.1. Memory                                    | 17   |

| 2.1.1. Definitions                             | 17   |

| 2.1.2. A few elements of technology            | 19   |

| 2.2. The processor                             | 20   |

| 2.2.1. Functional units                        | 20   |

| 2.2.2. Processor registers                     | 21   |

| 2.2.3. The elements of the processing unit     | 26   |

| 2.2.4. The elements of the control unit        | 28   |

| 2.2.5. The address calculation unit            | 29   |

| 2.3. Communication between modules             | 30   |

|                                                | 31   |

| 2.3.1. The PCI bus                             | 31   |

| Chapter 3. The Representation of Information   | 35   |

| 3.1 Review                                     | 36   |

#### vi Computer Architecture

| 3.1.1. Base 2                                                      | 36 |

|--------------------------------------------------------------------|----|

| 3.1.2. Binary, octal and hexadecimal representations               | 37 |

| 3.2. Number representation conventions                             | 38 |

| 3.2.1. Integers                                                    | 38 |

| 3.2.2. Real numbers                                                | 40 |

| 3.2.3. An example of a floating-point representation, the IEEE-754 |    |

| standard                                                           | 44 |

| 3.2.4. Dynamic range and precision                                 | 46 |

| 3.2.5. Implementation                                              | 47 |

| 3.2.6. Extensions of the IEEE-754 standard                         | 47 |

| 3.3. Character representation                                      | 48 |

| 3.3.1. 8-bit representation                                        | 48 |

| 3.3.2. Modern representations                                      | 50 |

| 3.4. Exercises                                                     | 52 |

| 2.1.2.1.2.1.2.1.2.1.2.1.2.1.2.1.2.1.2.1                            | -  |

| PART 2. PROGRAMMING MODEL AND OPERATION                            | 55 |

|                                                                    |    |

| Chapter 4. Instructions                                            | 57 |

| 4.1. Programming model                                             | 58 |

| 4.1.1. The registers of the I8086                                  | 58 |

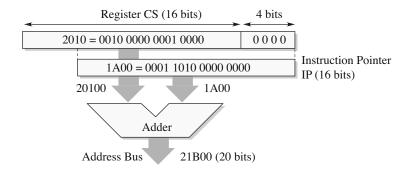

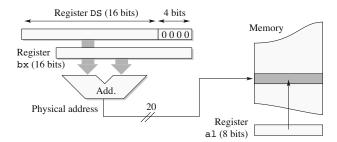

| 4.1.2. Address construction and addressing modes                   | 59 |

| 4.2. The set of instructions                                       | 62 |

| 4.2.1. Movement instructions                                       | 62 |

| 4.2.2. Arithmetic and logic instructions                           | 62 |

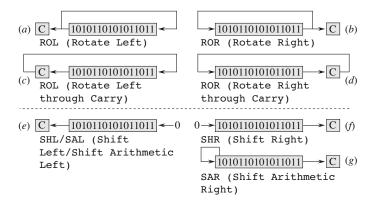

| 4.2.3. Shift instructions                                          | 64 |

| 4.2.4. Branching                                                   | 65 |

| 4.2.5. Other instructions                                          | 67 |

| 4.3. Programming examples                                          | 68 |

| 4.4. From assembly language to basic instructions                  | 70 |

| 4.4.1. The assembler                                               | 70 |

| 4.4.2. The assembly phases                                         | 72 |

| 4.4.3. The linker                                                  | 73 |

| 4.4.4. When to program in assembly language                        | 74 |

|                                                                    |    |

| Chapter 5. The Processor                                           | 75 |

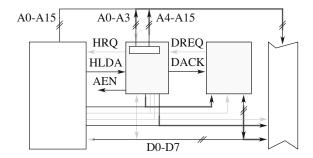

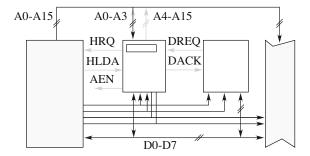

| 5.1. The control bus                                               | 76 |

| 5.1.1. Reset line                                                  | 77 |

| 5.1.2. Hold line                                                   | 77 |

| 5.1.3. Wait control line                                           | 78 |

| 5.1.4. Interrupt lines                                             | 78 |

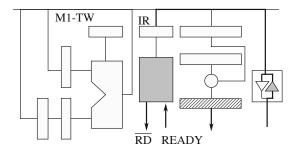

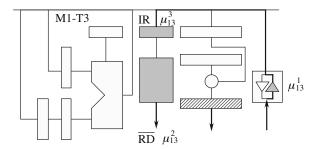

| 5.1.5. Conceptual diagram                                          | 78 |

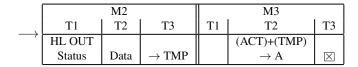

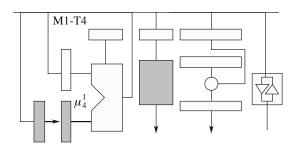

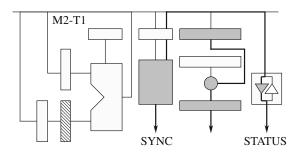

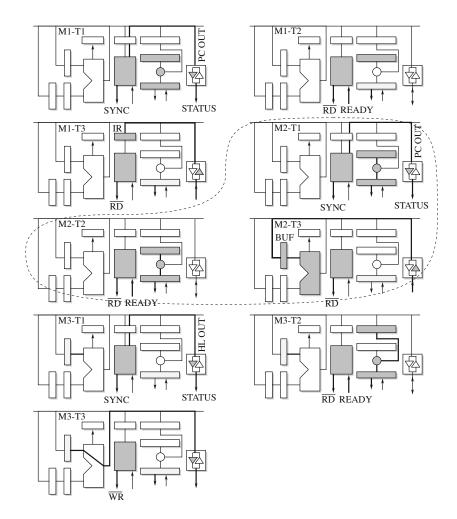

| 5.2. Execution of an instruction: an example                       | 79 |

| 5.2.1. Execution of the instruction                                | 81 |

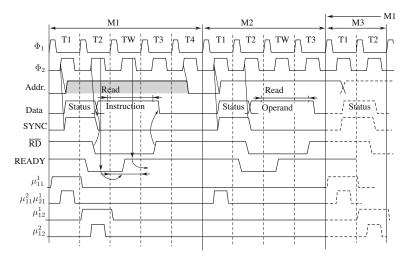

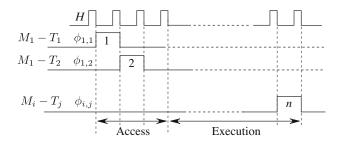

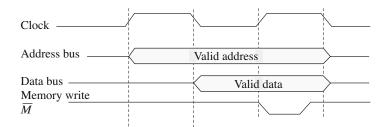

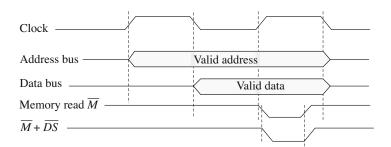

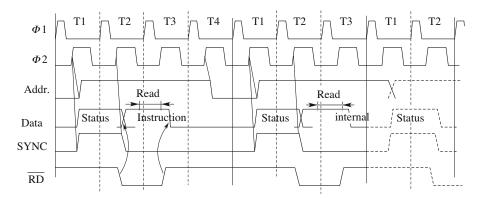

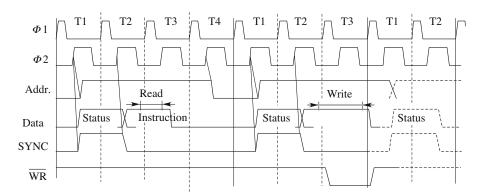

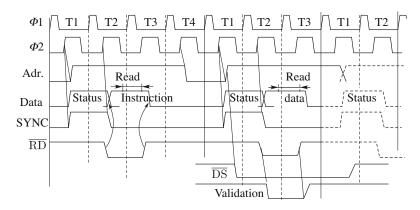

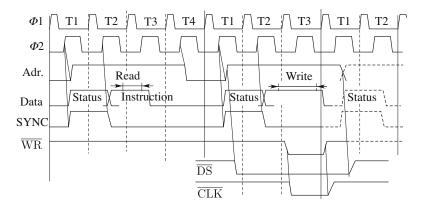

|    | 5.2.2. Timing diagram                        | 85  |

|----|----------------------------------------------|-----|

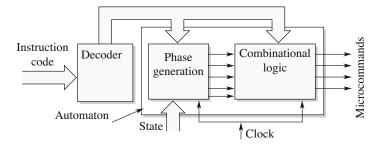

|    | 5.3. Sequencer composition                   | 87  |

|    | 5.3.1. Traditional synthesis methods         | 87  |

|    | 5.3.2. Microprogramming                      | 90  |

|    | 5.4. Extensions                              | 91  |

|    | 5.4.1. Coprocessors                          | 91  |

|    | 5.4.2. Vector extensions                     | 94  |

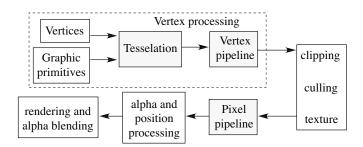

|    | 5.4.3. DSP and GPU                           | 99  |

|    | 5.5. Exercise                                | 101 |

| C  | hapter 6. Inputs and Outputs                 | 103 |

| C. |                                              |     |

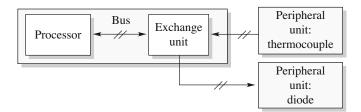

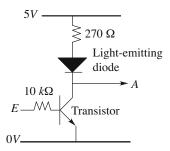

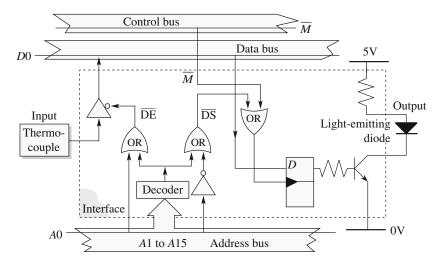

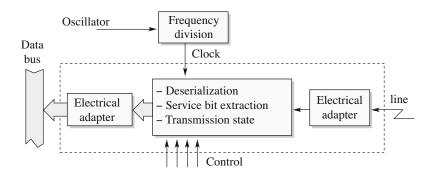

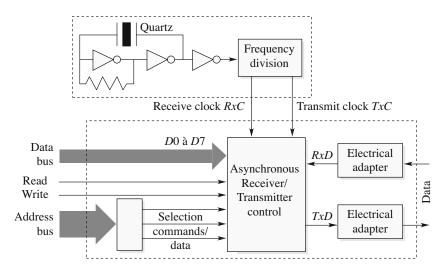

|    | 6.1. Examples                                | 105 |

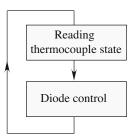

|    | 6.1.1. Example: controlling a thermocouple   | 105 |

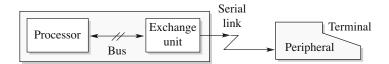

|    | 6.1.2. Example: serial terminal connection   | 111 |

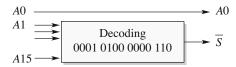

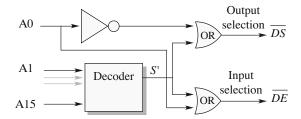

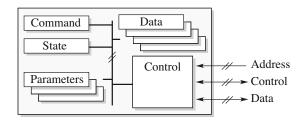

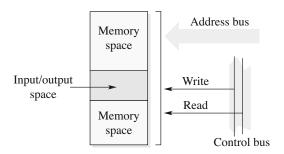

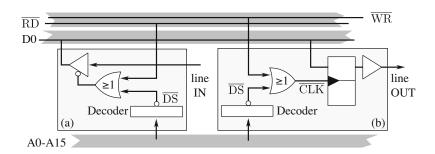

|    | 6.2. Design and addressing of EU             | 115 |

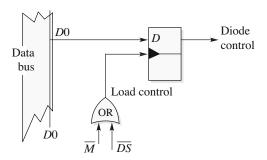

|    | 6.2.1. Design of exchange units              | 115 |

|    | 6.2.2. Exchange unit addressing              | 116 |

|    | 6.3. Exchange modes                          | 118 |

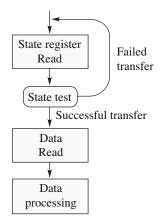

|    | 6.3.1. The polling exchange mode             | 118 |

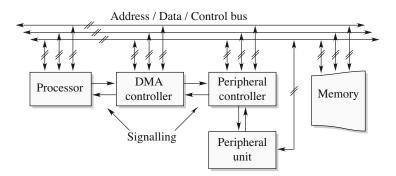

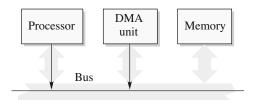

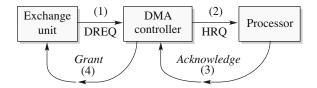

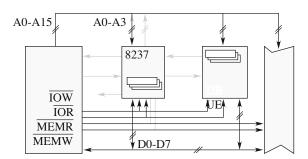

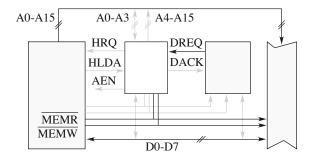

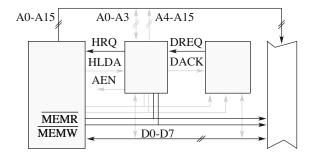

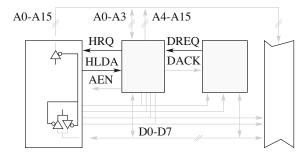

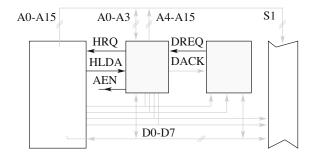

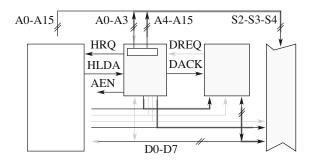

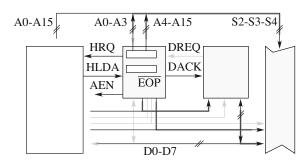

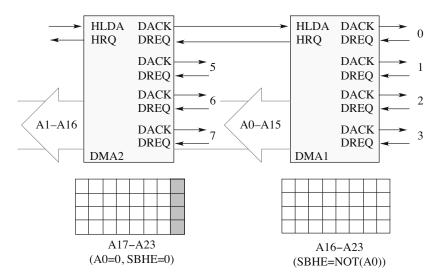

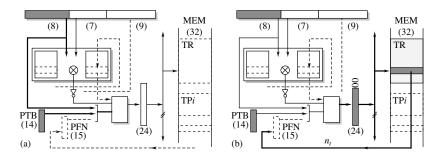

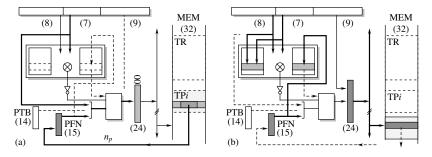

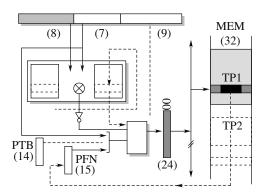

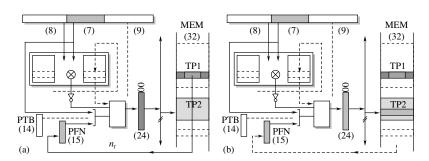

|    | 6.3.2. Direct memory access                  | 119 |

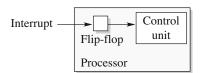

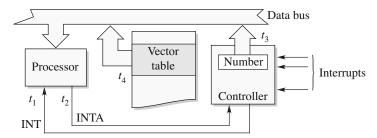

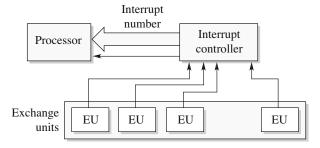

|    | 6.3.3. Interrupts                            | 126 |

|    | 6.4. Handling interrupts                     | 127 |

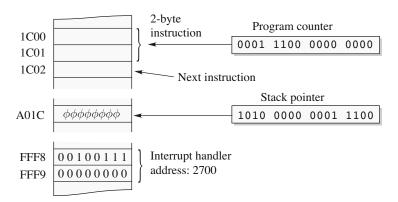

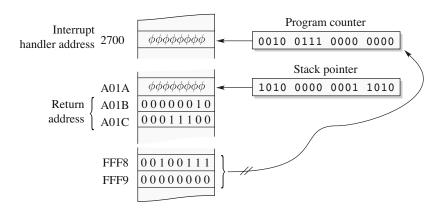

|    | 6.4.1. Operating principle                   | 127 |

|    | 6.4.2. Examples                              | 129 |

|    | 6.4.3. Software interrupts                   | 131 |

|    | 6.4.4. Masking and unmasking interrupts      | 131 |

|    | 6.4.5. Interrupt priorities or levels        | 131 |

|    |                                              | 132 |

|    | 6.4.6. Similar mechanisms                    |     |

|    | 6.5. Exercises                               | 133 |

| P  | ART 3. MEMORY HIERARCHY                      | 137 |

| C  | hapter 7. Memory                             | 139 |

|    | 7.1. The memory resource                     | 139 |

|    | 7.2. Characteristics                         | 140 |

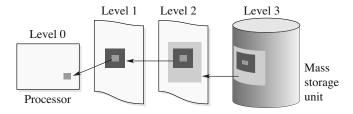

|    | 7.3. Memory hierarchy                        | 141 |

|    | 7.3.1. Principle of locality                 | 142 |

|    | 7.3.2. Hierarchy organization and management | 143 |

|    | 7.3.3. Definitions and performance           | 144 |

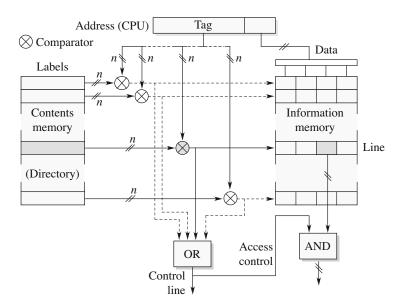

|    | 7.4. Memory size and protection              | 145 |

|    | 7.4. Memory size and protection              | 145 |

|    |                                              | 143 |

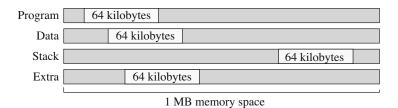

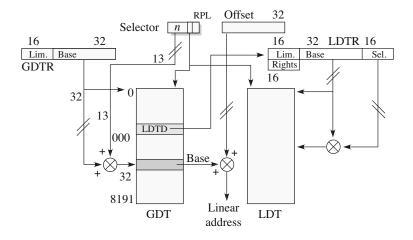

|    | 7.5.1. Using segment registers: an example   | 140 |

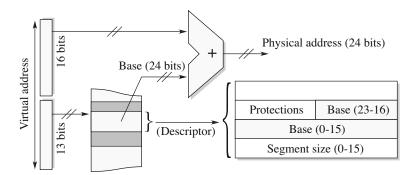

|    | L.D.Z. USING SEGMENT DESCRIPTIONS            | 14/ |

#### viii Computer Architecture

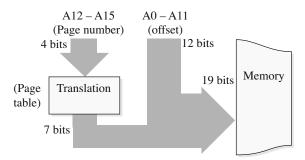

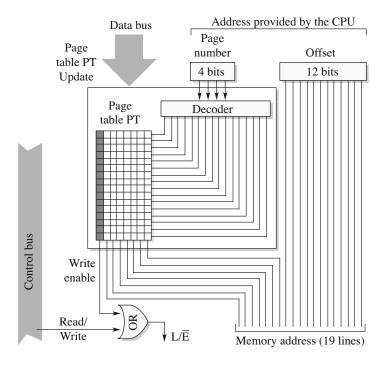

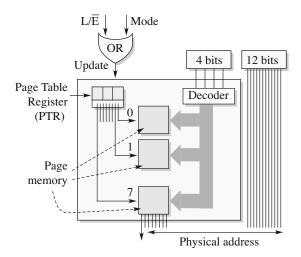

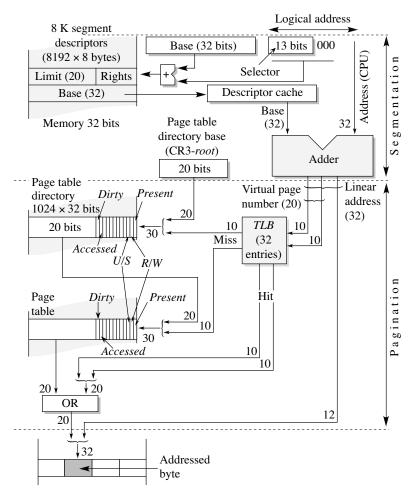

| 7.6. Paging                                              | 148        |

|----------------------------------------------------------|------------|

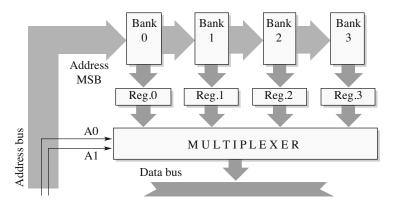

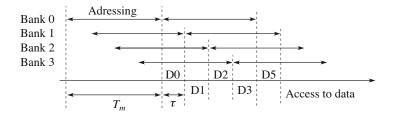

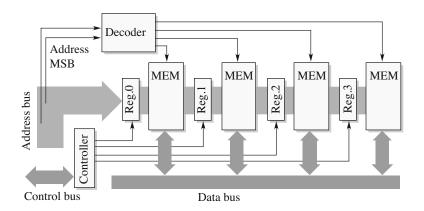

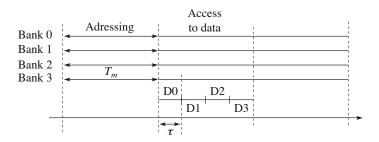

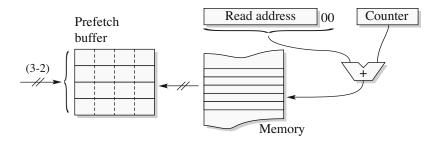

| 7.7. Memory interleaving and burst mode                  | 151        |

| 7.7.1. C-access                                          | 151        |

| 7.7.2. S-access                                          | 151        |

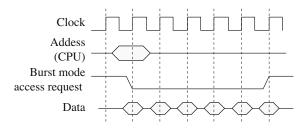

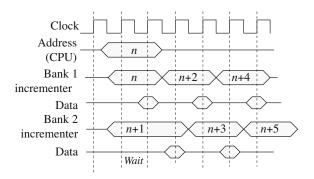

| 7.7.3. Burst mode                                        | 153        |

| 7.7.4. Prefetch buffers                                  | 153        |

| 7.8. Protections, example of the I386                    | 154        |

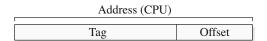

| Chapter 8. Caches                                        | 157        |

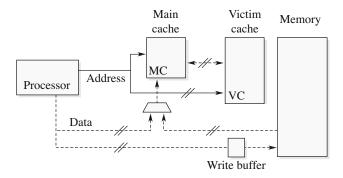

| 8.1. Cache memory                                        | 157        |

|                                                          |            |

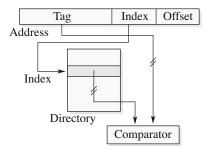

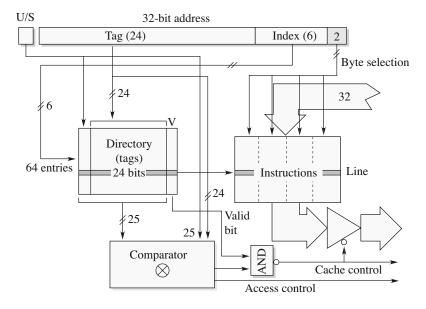

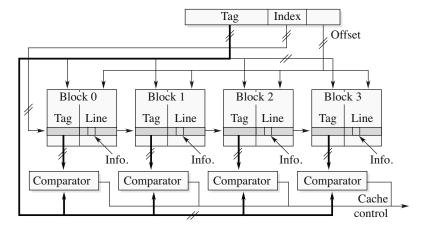

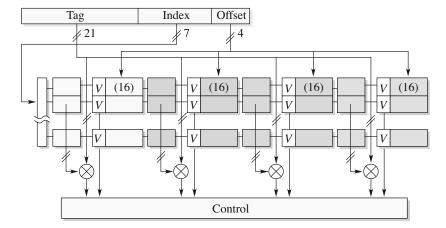

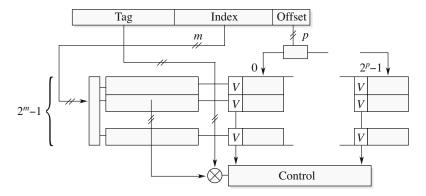

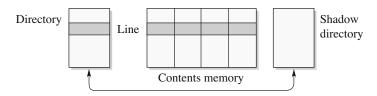

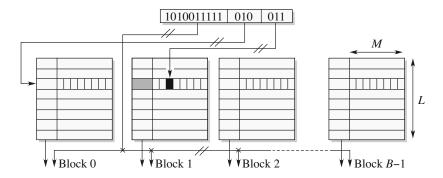

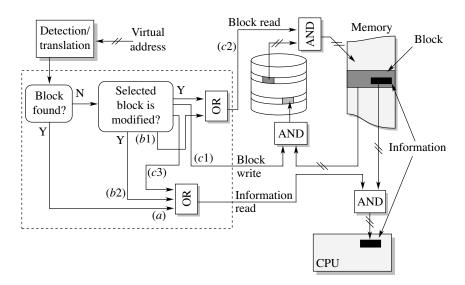

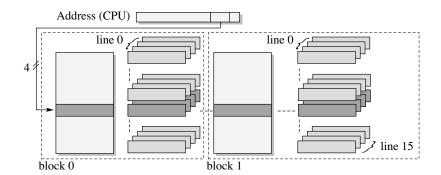

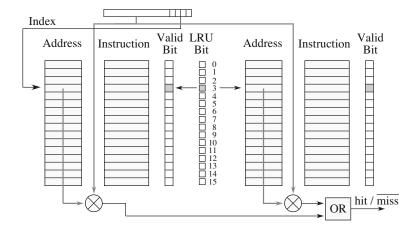

| 8.1.1. Operating principle and architectures             | 157<br>158 |

| 8.1.2. Cache memory operation                            |            |

| 8.1.3. Cache design                                      | 160        |

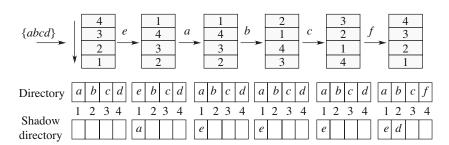

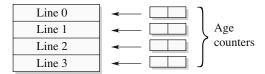

| 8.2. Replacement algorithms                              | 165        |

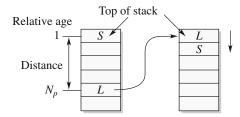

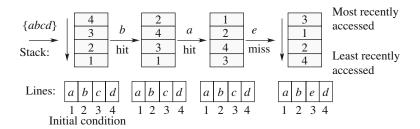

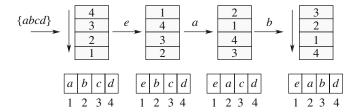

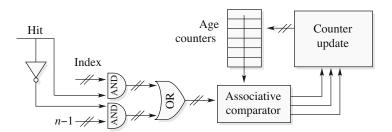

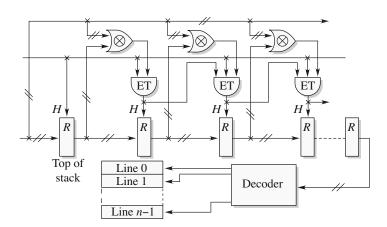

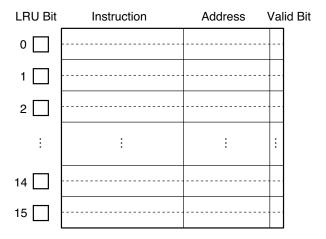

| 8.2.1. The LRU method                                    | 165        |

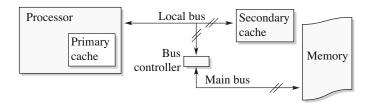

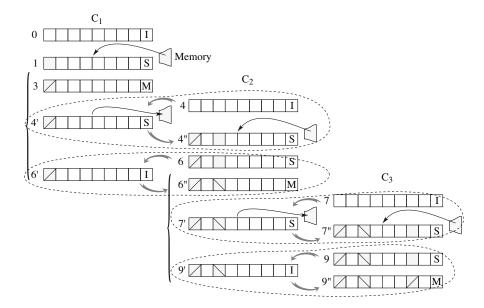

| 8.2.2. The case of several levels of cache               | 171        |

| 8.2.3. Performance and simulation                        | 172        |

| Chapter 9. Virtual Memory                                | 175        |

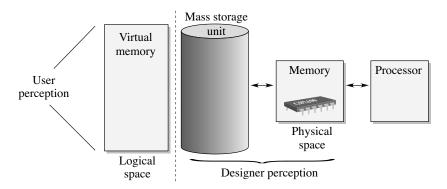

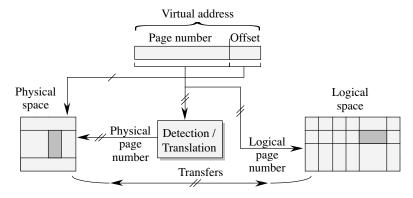

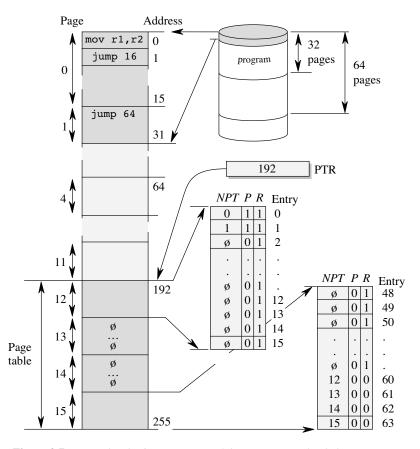

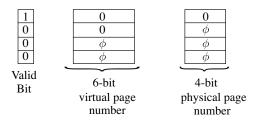

| 9.1. General concept                                     | 176        |

| 9.1.1. Operation                                         | 176        |

| 9.1.2. Accessing information                             | 176        |

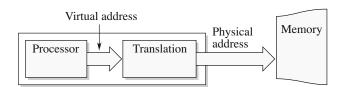

| 9.1.3. Address translation                               | 177        |

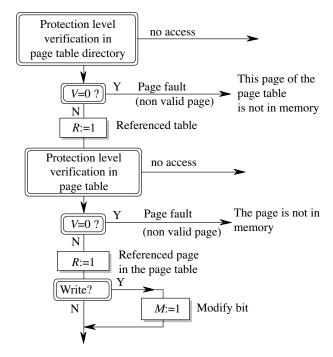

| 9.2. Rules of the access method                          | 178        |

| 9.2.1. Page fault                                        | 178        |

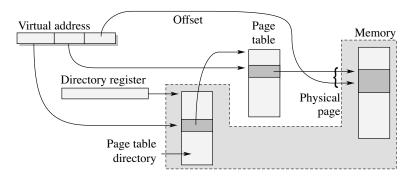

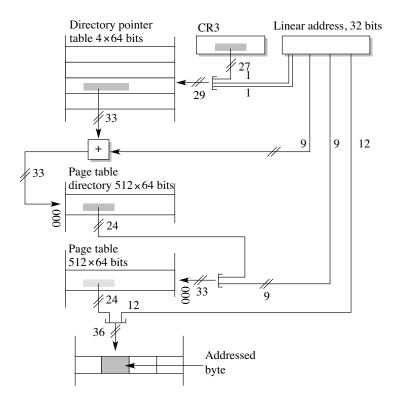

| 9.2.2. Multi level paging                                | 179        |

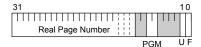

| 9.2.3. Service information, protection and access rights | 180        |

| 9.2.4. Page size                                         | 181        |

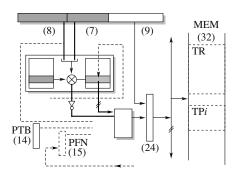

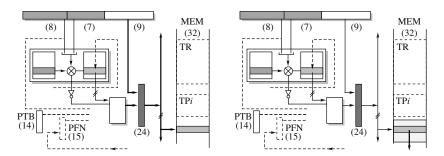

| 9.3. Example of the execution of a program               | 182        |

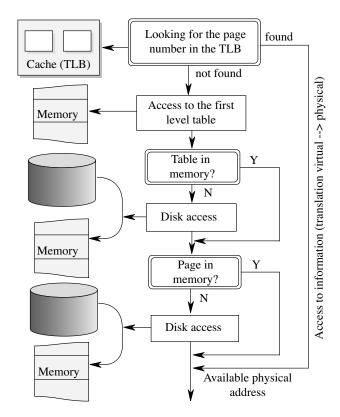

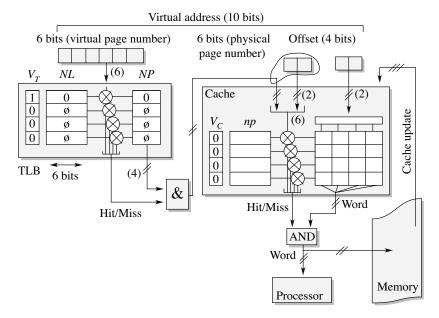

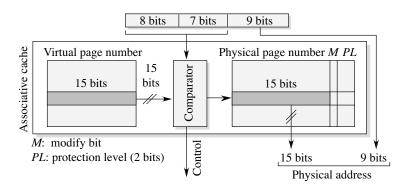

| 9.3.1. Introducing the translation cache                 | 184        |

|                                                          | 184        |

| 9.3.2. Execution                                         |            |

| 9.3.3. Remarks                                           | 187<br>188 |

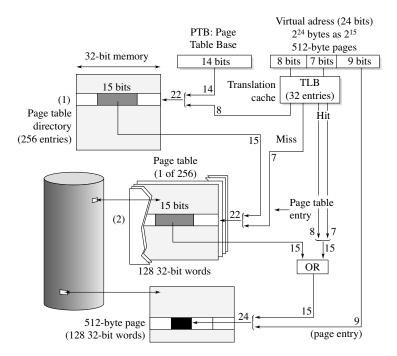

| 9.4. Example of two-level paging                         |            |

| 9.4.1. Management                                        | 188        |

| 9.4.2. Handling service bits                             | 190        |

| 9.4.3. Steps in the access to information                | 190        |

| 9.5. Paged segmentation                                  | 194        |

| 9.5.1. 36-bit extensions                                 | 196        |

| 9.6. Exercise                                            | 197        |

| 9.7. Documentation excerpts                              | 198        |

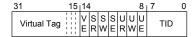

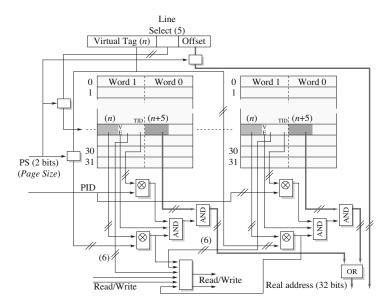

| 9.7.1. Introduction to the MMU                           | 198        |

| 9.7.2. Description of the TLB                            | 199        |

| 9.7.3. TLB features                                      | 202        |

| PART 4. PARALLELISM AND PERFORMANCE ENHANCEMENT    | 205 |

|----------------------------------------------------|-----|

| Chapter 10. Pipeline Architectures                 | 207 |

| 10.1. Motivations and ideas                        | 207 |

| 10.1.1. RISC machines                              | 207 |

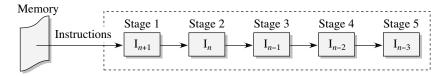

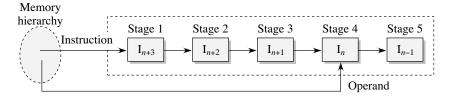

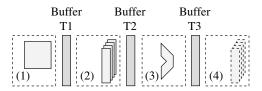

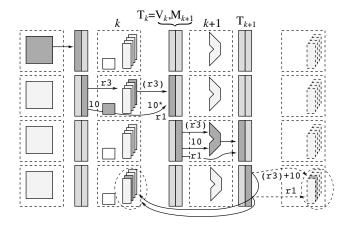

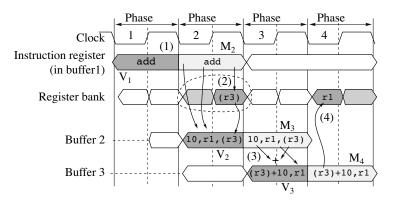

| 10.1.2. Principle of operation                     | 209 |

| 10.1.3. Cost of the pipeline architecture          | 211 |

| 10.2. Pipeline management problems                 | 212 |

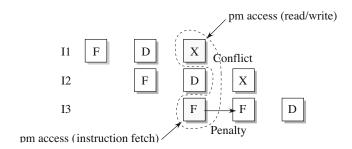

| 10.2.1. Structural hazards                         | 212 |

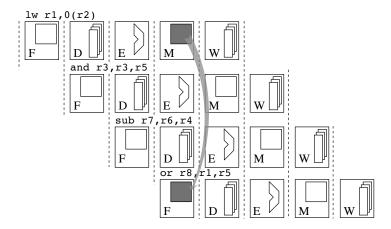

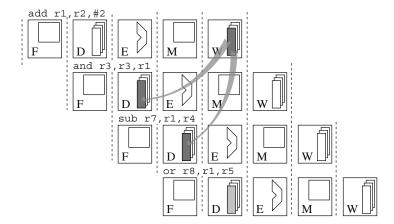

| 10.2.2. Dependency conflicts                       | 216 |

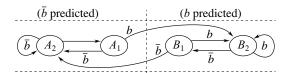

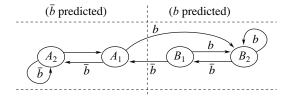

| 10.2.3. Branches                                   | 217 |

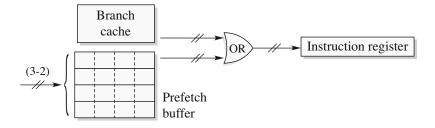

| 10.2.3. Handling branches                          | 218 |

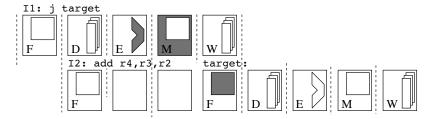

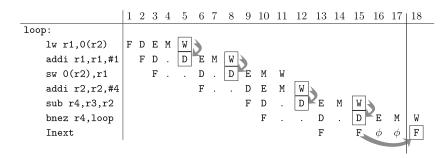

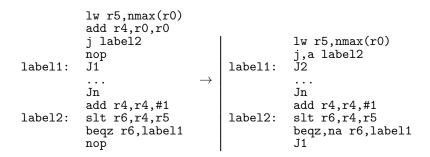

| 10.3.1. Delayed branches and software handling     | 218 |

|                                                    | 210 |

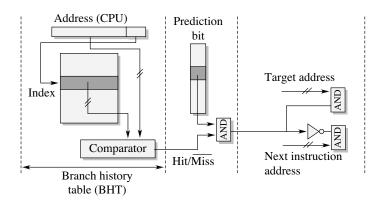

| 10.3.2. Branch predictions                         | 225 |

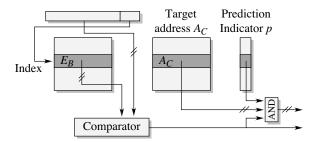

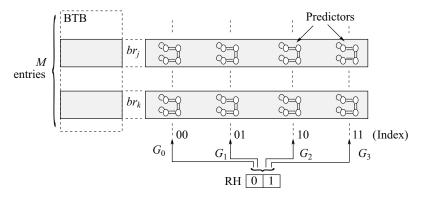

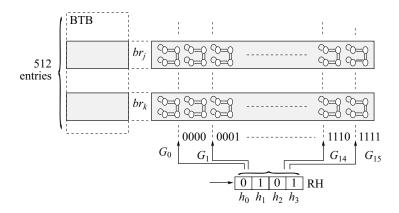

| 10.3.3. Branch target buffer                       |     |

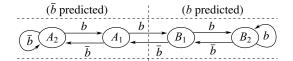

| 10.3.4. Global prediction                          | 227 |

| 10.3.5. Examples                                   | 229 |

| 10.4. Interrupts and exceptions                    | 233 |

| 10.4.1. Interrupts                                 | 234 |

| 10.4.2. Traps and faults                           | 234 |

| Chapter 11. Example of an Architecture             | 235 |

| 11.1. Presentation                                 | 235 |

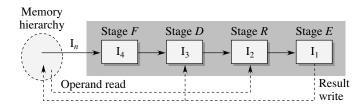

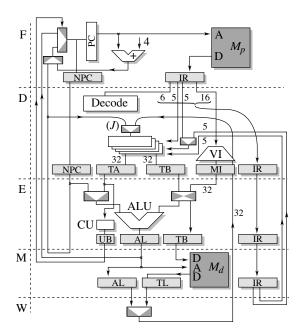

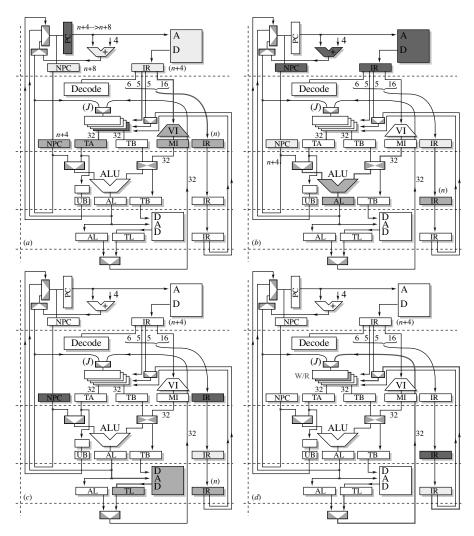

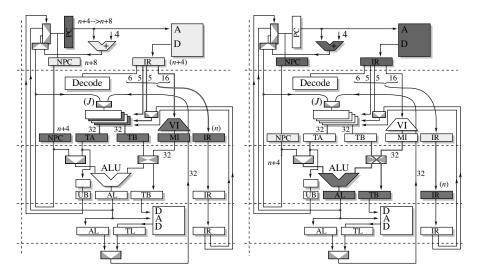

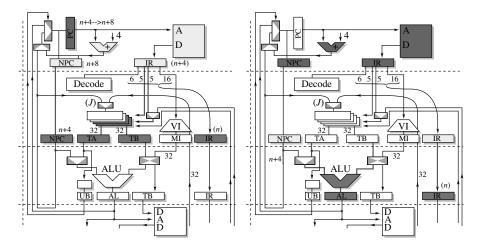

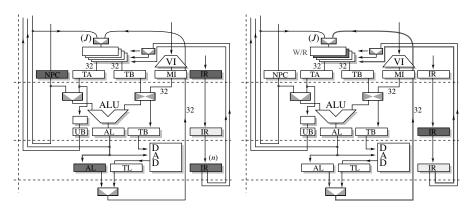

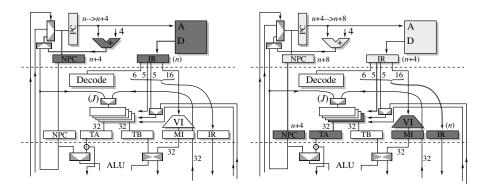

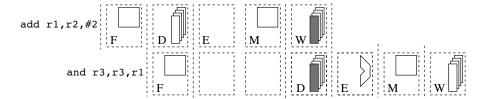

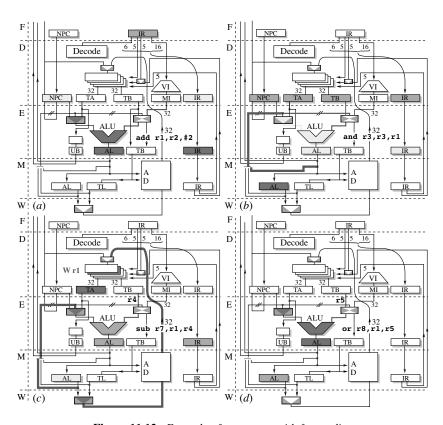

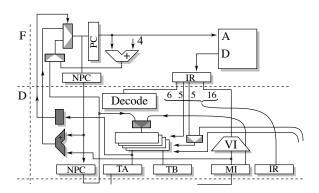

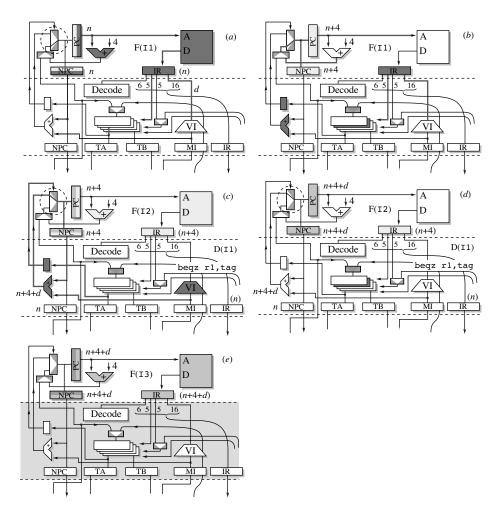

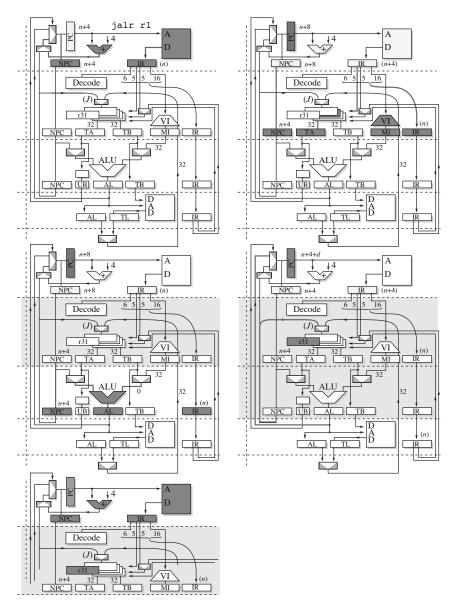

| 11.1.1. Description of the pipeline                | 235 |

| 11.1.2. The instruction set                        | 238 |

| 11.1.3. Instruction format                         | 239 |

| 11.2. Executing an instruction                     | 240 |

| 11.2.1. Reading and decoding an instruction        | 240 |

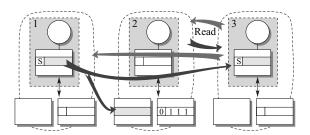

| 11.2.2. Memory read                                | 241 |

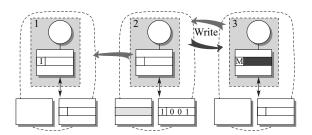

| 11.2.3. Memory write operations                    | 241 |

| 11.2.4. Register to register operations            | 242 |

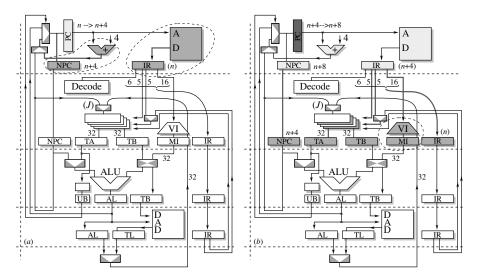

| 11.2.5. Conditional branching                      | 243 |

| 11.2.6. Instruction with immediate addressing      | 246 |

| 11.3. Conflict resolution in the DLX               | 246 |

| 11.3. Conflict resolution in the DLA               | 240 |

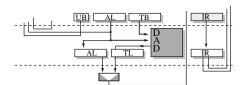

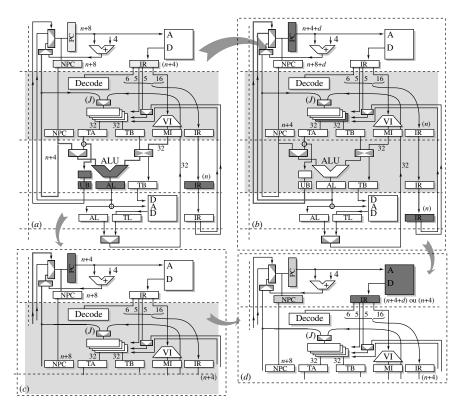

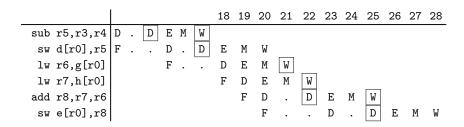

| 11.3.1. Forwarding techniques                      | 247 |

| 11.3.2. Handling branches                          |     |

| 11.4. Exercises                                    | 252 |

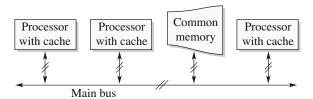

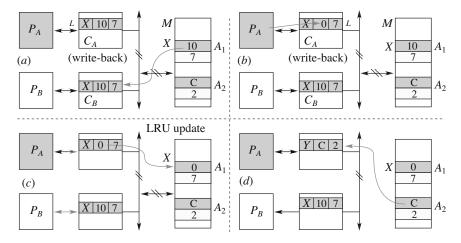

| Chapter 12. Caches in a Multiprocessor Environment | 261 |

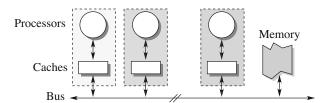

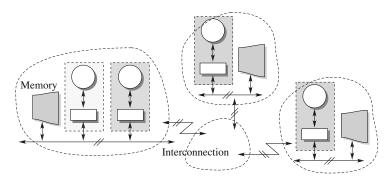

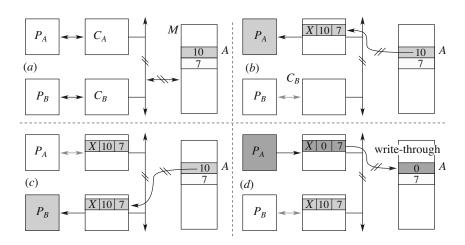

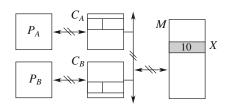

| 12.1. Cache coherence                              | 262 |

| 12.1.1. Examples                                   |     |

| 12.1.2. The elements to consider                   |     |

#### x Computer Architecture

| 12.1.3. Definition of coherence             | 264 |

|---------------------------------------------|-----|

| 12.1.4. Methods                             | 265 |

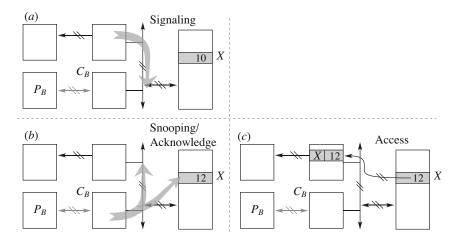

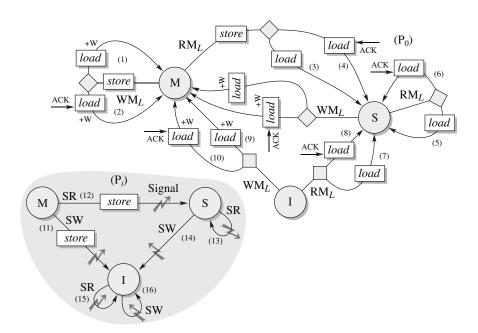

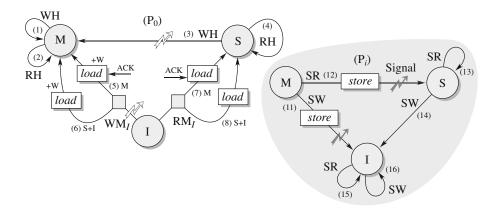

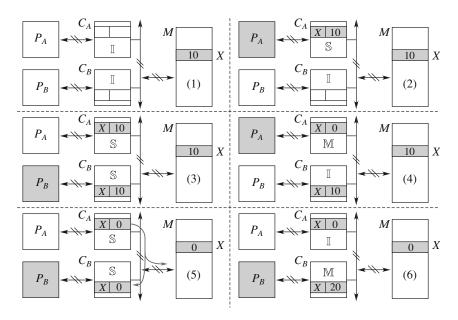

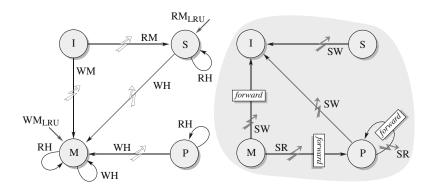

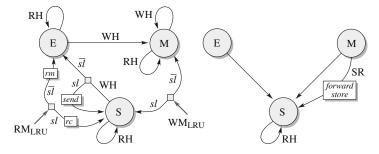

| 12.2. Examples of snooping protocols        | 267 |

| 12.2.1. The MSI protocol                    | 267 |

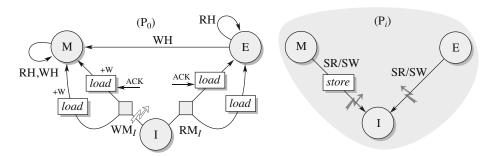

| 12.2.2. The MEI protocol                    | 270 |

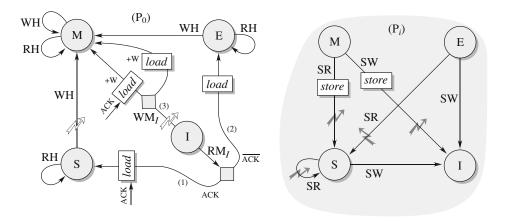

| 12.2.3. The MESI protocol                   | 271 |

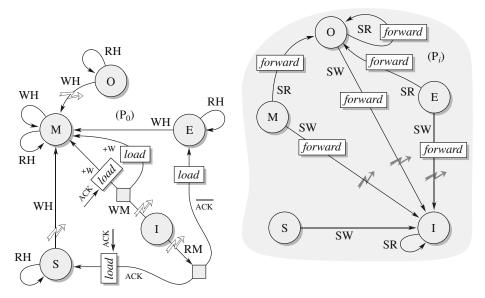

| 12.2.4. The MOESI protocol                  | 273 |

| 12.3. Improvements                          | 275 |

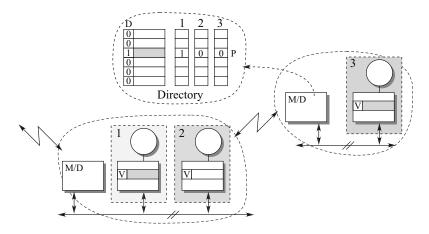

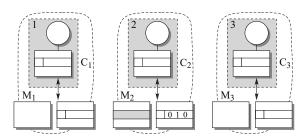

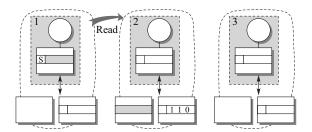

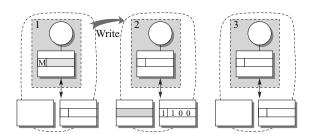

| 12.4. Directory-based coherence protocols   | 275 |

| 12.5. Consistency                           | 278 |

| 12.5.1. Consistency and coherence           | 278 |

| 12.5.2. Notations                           | 279 |

| 12.5.3. Atomic consistency                  | 280 |

| 12.5.4. Sequential consistency              | 281 |

| 12.5.5. Causal consistency                  | 282 |

| 12.5.6. Weak consistency                    | 283 |

| 12.6. Exercises                             | 284 |

| 12.0. LACICISCS                             | 207 |

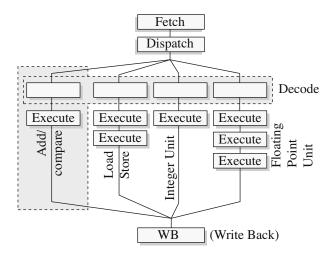

| Chapter 13. Superscalar Architectures       | 287 |

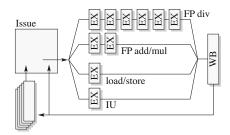

| 13.1. Superscalar architecture principles   | 287 |

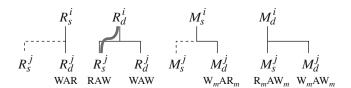

| 13.1.1. Hazards                             | 288 |

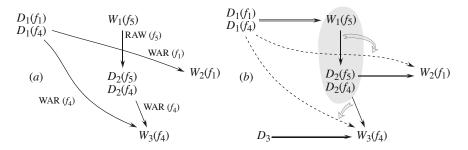

| 13.2. Seeking solutions                     | 290 |

| 13.2.1. Principles                          | 290 |

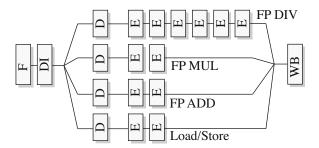

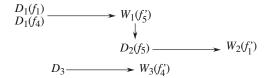

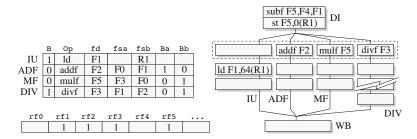

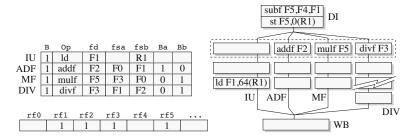

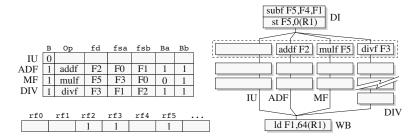

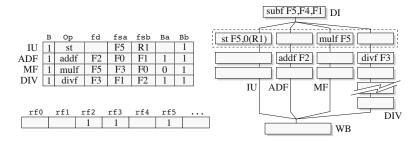

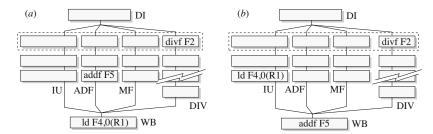

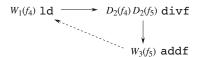

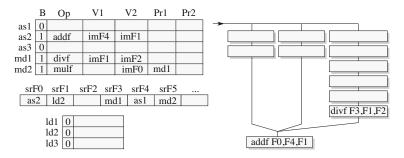

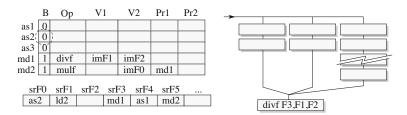

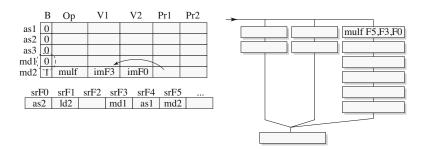

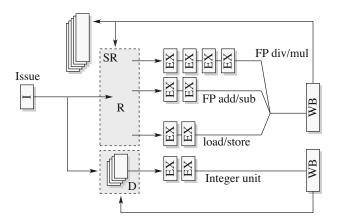

| 13.2.2. Example                             | 293 |

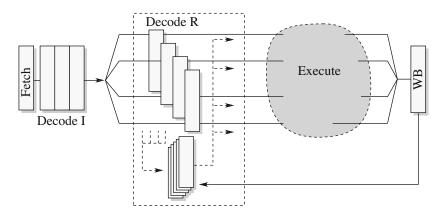

| 13.3. Handling the flow of instructions     | 295 |

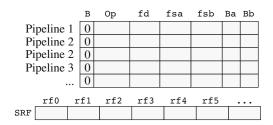

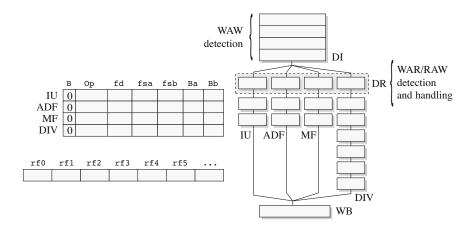

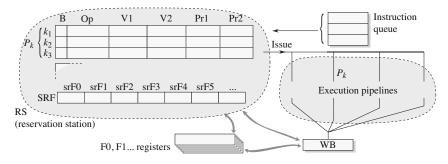

| 13.3.1. Principle of scoreboarding          | 295 |

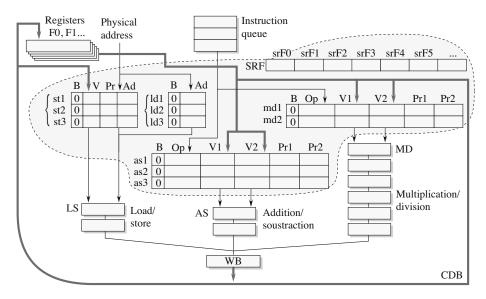

| 13.3.2. Scoreboarding implementation        | 296 |

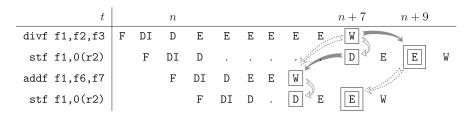

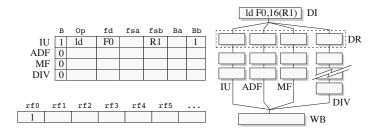

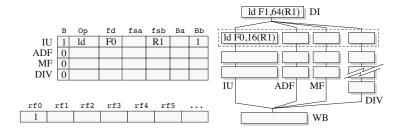

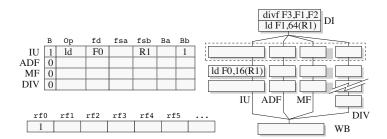

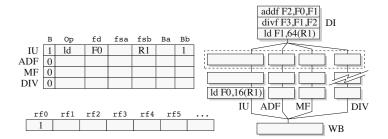

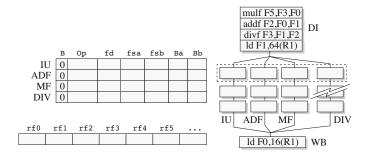

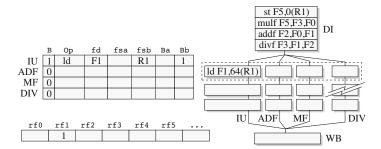

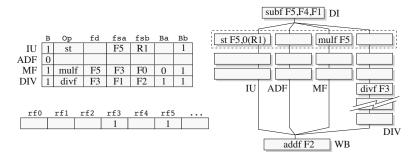

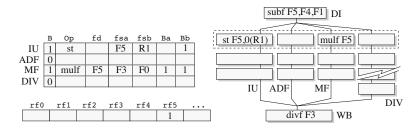

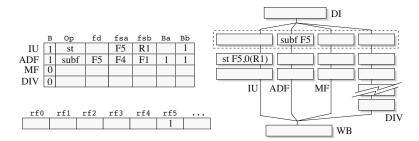

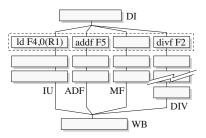

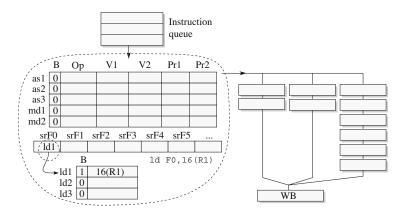

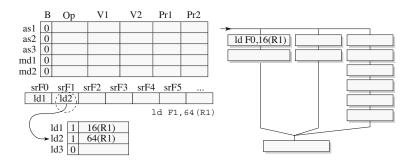

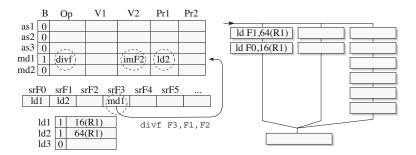

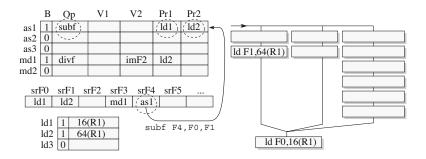

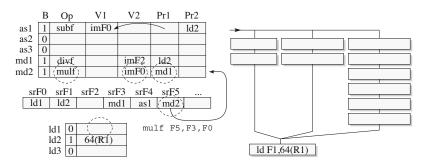

| 13.3.3. Detailed example                    | 297 |

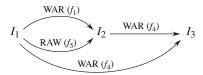

| 13.3.4. Comments on precedence constraints  | 302 |

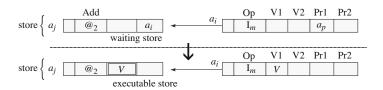

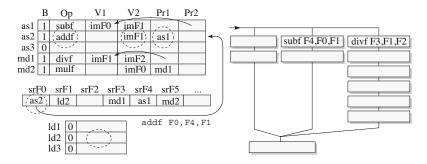

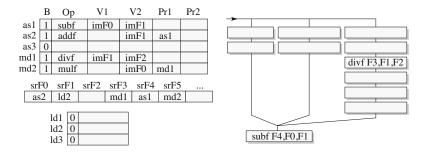

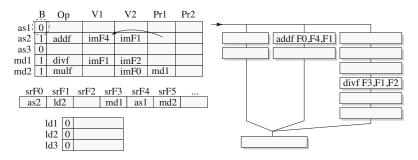

| 13.3.5. Principle of the Tomasulo algorithm | 303 |

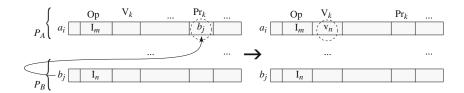

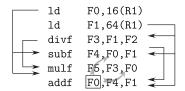

| 13.3.6. Detailed example                    | 306 |

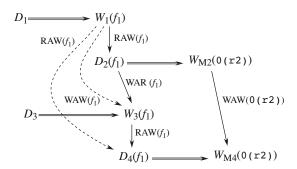

| 13.3.7. Loop execution and WAW hazards      | 313 |

|                                             | 315 |

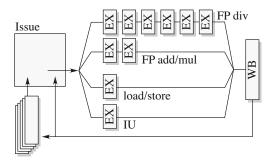

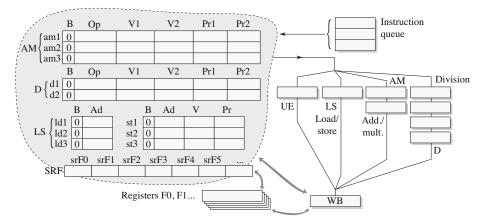

| 13.4. VLIW architectures                    |     |

| 13.4.1. Limits of superscalar architectures | 315 |

| 13.4.2. VLIW architectures                  | 316 |

| 13.4.3. Predication                         | 317 |

| 13.5. Exercises                             | 321 |

| PART 5. APPENDICES                          | 325 |

| Appendix A. Hints and Solutions             | 327 |

| A1.1. The representation of information     | 327 |

| A1.1. The representation of information     | 330 |

| Table of Contents | xi |  |

|-------------------|----|--|

|-------------------|----|--|

| A1.3. Inputs and outputs                      | 331 |

|-----------------------------------------------|-----|

|                                               |     |

| ,,,                                           | 333 |

| A1.5. Pipeline architectures                  | 335 |

| A1.6. Caches in a multiprocessor environment  | 341 |

| A1.7. Superscalar architectures               | 344 |

| Appendix B. Programming Models                | 347 |

| A2.1. Instruction coding in the I8086         | 347 |

| A2.2. Instruction set of the DLX architecture | 349 |

| A2.2.1. Operations on floating-point numbers  | 349 |

| A2.2.2. Move operations                       | 349 |

| A2.2.3. Arithmetic and logic operations       | 350 |

| A2.2.4. Branches                              | 350 |

| Bibliography                                  | 351 |

| Index                                         | 357 |

#### **Preface**

This book presents the concepts necessary for understanding the operation of a computer. The book is written based on the following:

- the details of how a computer's components function electronically are beyond the scope of this book;

- the emphasis is on the concepts and the book focuses on the building blocks of a machine's architecture, on their functions, and on their interaction;

- the essential links between software and hardware resource are emphasized wherever necessary.

For reasons of clarity, we have deliberately chosen examples that apply to machines from all eras, without having to water down the contents of the book. This choice helps us to show how techniques, concepts and performance have evolved since the first computers.

This book is divided into five parts. The first four, which are of increasing difficulty, form the core of the book: "Elements of a basic architecture", "Programming model and operation", "Memory hierarchy" and "Parallelism and performance enhancement". The final part, which comprises appendices, provides hints and solutions to the exercises in the book as well as programming models. The reader may approach each part independently based on their prior knowledge and goals.

Presentation of the five parts:

- 1) Elements of a basic architecture:

- Chapter 1 takes a historical approach to present the main building blocks of a processor.

- Chapter 2 lists in detail the basic modules and their features, and describes how they are connected.

- Chapter 3 focuses on the representation of information: integers, floating-point numbers, fixed-point numbers and characters.

- 2) Programming model and operation:

- Chapter 4 explains the relationship between the set of instructions and the architecture.

- Chapter 5 provides a detailed example of the execution of an instruction to shed some light on the internal mechanisms that govern the operation of a processor. Some additional elements, such as coprocessors and vector extensions, are also introduced.

- Chapter 6 describes the rules polling, direct memory accesses and interrupts involved in exchanges with peripherals.

- 3) Memory hierarchy:

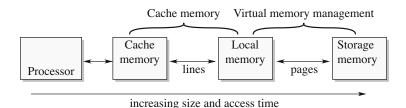

- Chapter 7 gives some elements hierarchy, segmentation and paging on the organization of memory.

- Chapter 8 presents cache memory organization and access methods.

- Chapter 9 describes virtual memory management concepts, rules and access rights.

- 4) Parallelism and performance enhancement:

- Chapter 10 gives an introduction to parallelism by presenting pipeline architectures: concepts, as well as software and hardware conflict resolution.

- Chapter 11 gives the DLX architecture as an example.

- Chapter 12 deals with cache management in a multiprocessor environment; coherence and protocols (MSI, MEI, etc.).

- Chapter 13 presents the operation of a superscalar architecture conflict, the scoreboarding and Tomasulo algorithms, and VLIW architectures.

- 5) Complementary material on the programming models used and the hints and solutions to the exercises given in the different chapters can be found in the appendices.

# PART 1 Elements of a Basic Architecture

# Chapter 1

# Introduction

After providing some historical background, we will highlight the major components of a *computer* machine [MOR 81, ROS 69, LAV 75]. This will lead us to describe a category of calculators that we will refer to as *classic architecture machines*, or *classic architecture uniprocessors*. We will examine the functions performed by each of their modules, and then describe them in greater detail in the following chapters.

#### 1.1. Historical background

#### 1.1.1. Automations and mechanical calculators

The first known mechanical calculators [SCI 96] were designed by Wilhelm Schickard (1592–1635) ( $\approx$ 1623), Blaise Pascal ( $\approx$ 1642) and Gottfried Wilhelm Leibniz (1646–1716) ( $\approx$ 1673): they operate in base 10 through a gear mechanism.

Figure 1.1. Blaise Pascal's Pascaline

#### 4 Computer Architecture

It is up to the user to put together series of operations. The need for a sequence of processes that is automated is what will eventually lead to the design of computers.

The sequencing of simple tasks had already been implemented in the design of music boxes, barrel organs, self-playing pianos, in which cylinders with pins, cam systems and perforated paper tapes determined the melody. The loom, designed by Joseph-Marie Jacquard (1752–1834), is another example of an automaton. A series of perforated cards indicates the sequence of elementary operations to perform: each hole allows a needle to go through, and the tetrahedron that supports the cards rotates at the same pace as the shuttle which carries the thread that is woven. Introduced in the years 1804–1805, Jacquard's invention was formally recognized by France as being of a public benefit in 1806. In 1812, there were 11,000 such looms in France [ENC 08]. Some can still be found in operation in workshops around Lyon.

Figure 1.2. An example of Jacquard's loom, courtesy of "La Maison des Canuts", Lyon, France

This system provides a first glance at what will later become devices based on programmable automatons, or calculators, dedicated to controlling industrial processes.

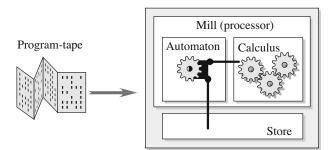

Charles Babbage (1792–1871) was the first to undertake the design of a machine combining an automaton and a mechanical calculator. Having already designed a calculator, the Difference Engine, which can be seen at the Science Museum in London, he presented a project for a more universal machine, at a seminar held in Turin in 1841. His collaboration with Ada Lovelace (the daughter of Lord Byron) allowed him to describe a more detailed and ambitious machine, which foreshadows our modern computers. This machine, known as the analytical engine [MEN 42], autonomously performs sequences of arithmetic operations. As with Jacquard's loom, it is controlled by perforated tape. The user describes on this "program-tape" the sequence of operations that needs to be performed by the machine. The tape is fed into the machine upon each new execution. This is because Babbage's machine, despite its ability to memorize intermediate results, had no means for memorizing programs, which were always on some external support. This is known as an external program machine. This machine introduces the concept of memory (referred to by Babbage as the store) and of a processor (the mill). Another innovation, and contrary to what was done before, is that the needles, which engaged based on the presence or the absence of holes in the perforated tape, do not directly engage the *output devices*. In a barrel organ, a note is associated with each hole in the tape; this is formally described by saying that the output is logically equal to the input. In the analytical engine, however, we can already say that a program and data are coded.

Figure 1.3. Babbage's analytical engine

This machine is divided into three distinct components, with different functions: the *automaton–calculator* part, the *data* and the *program*.

While each row of the perforated tape contains data that are "logical" in nature – the presence or the absence of a hole - the same cannot be said for both the automaton, which is purely mechanical, and the calculation unit, which operates on base 10 representations.

#### 1.1.1.1. Data storage

The idea that it was necessary to automatically process data took hold during the 1890 census in the United States, a census that covered 62 million people. It was the

#### 6 Computer Architecture

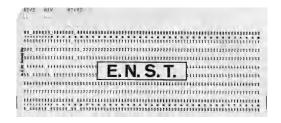

subject of a call for bids, with the contract going to Herman Hollerith (1860–1929). Hollerith suggested using a system of perforated cards already used by certain railway companies. The cards were 7.375 by 3.25 inches which, as the legend goes, correspond to the size of the \$1 bill at the time. The *Tabulating Machine Company*, started by Herman Hollerith, would eventually become *International Business Machines* (IBM), in 1924.

Figure 1.4. A perforated card: each character is coded according to the "Hollerith" code

In 1937, Howard Aiken, of Harvard University, gave IBM the suggestion of building a giant calculator from the mechanical and electromechanical devices used for punch card machines. Completed in 1943, the machine weighed 10,000 pounds, was equipped with accumulators capable of memorizing 72 numbers, and could multiply two 23-digit numbers in 6 s. It was controlled through instructions coded onto perforated paper tape.

Figure 1.5. Perforated tape

Despite the knowledge acquired from Babbage, this machine lacked the ability to process conditional instructions. It did, however, have two additional features compared to Babbage's analytical engine: a clock for controlling sequences of operations and registers, a type of temporary memory used for recording data.

Another precursor was the *Robinson*, designed in England during World War II and used for decoding encrypted messages created by the German forces on *Enigma* machines.

#### 1.1.2. From external program to stored program

In the 1940s, research into automated calculators was a booming field, spurred in large part by A. Turing in England; H. Aiken, P. Eckert and J. Mauchly [MAU 79] in

the United States; and based in part on the works of J.V.Atanasoff (1995 $^{\dagger}$ ) (Automatic Electronic Digital Computer (AEDQ) between 1937 and 1942).

The first machines that were built were electromechanical, and later relied on vacuum tube technology. They were designed for specific processes and had to be rewired every time a change was required in the sequence of operations. These were still externally programmed machines. J. von Neumann [VON 45, GOL 63] built the foundations for the architecture used by modern calculators, the von Neumann architecture.

The first two principles that define this architecture are the following:

- The universal applicability of the machines.

- Just as intermediate results produced from the execution of operations are stored into memory, the operations themselves will be stored in memory. This is called stored-program computing.

The elementary operations will be specified by instructions, the instructions are listed in *programs* and the programs are stored in *memory*. The machine can now go through the steps in a program with no outside intervention, and without having to reload the program every time it has to be executed.

The third principle that makes this calculator an "intelligent" machine, as opposed to its ancestors, is the sequence break. The machine has decision capabilities that are independent from any human intervention: as the program proceeds through its different steps, the automaton decides the sequence of instructions to be executed, based on the results of tests performed on the data being processed. Subsequent machines rely on this basic organization.

Computer designers then focused their efforts in two directions:

- Technology: using components that are more compact, perform better, with more complex functions, and consume lower energy.

- Architecture: parallelization of the processor's activities and organization of the memory according to a hierarchy. Machines designed with a Harvard architecture, in which access to instructions and to data is performed independently, meet this condition in part.

Figure 1.6 presents the major dates and concepts in the evolution that led to what is now called a *computer*. Note that without the methodological foundation provided by Boolean algebra, the first computer would probably not have emerged so quickly. This is because the use of this algebra leads to a *unification* of the representations used for designing the components and coding the instructions and data.

Figure 1.6. From externally programmed to parallel computing

#### 1.1.3. The different generations

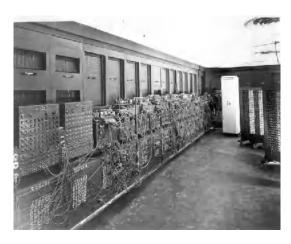

Since the *Electronic Discrete Variable Automatic Computer* (EDVAC) in 1945, under the direction of J. von Neumann [VON 45, GOL 63] (the first stored-program calculator), hundreds of machines have been designed. To organize the history of these machines, we can use the concept of *generations* of calculators, which is based essentially on technological considerations. Another classification could just as well be made based on software criteria, associated with the development of languages and operating systems for calculators.

#### 1.1.3.1. The first generation ( $\approx$ 1938–1953)

Machines of this era are closer to laboratory prototypes than computers as we picture them today. These machines consist of relays, electronic tubes, resistors and other discrete components. The ENIAC, for example, abbreviated form for *Electronic Numerical Integrator And Computer*, was made up of 18,000 vacuum tubes, consumed around 150 kW, and was equipped with 20 memory elements (Figure 1.7<sup>1</sup>).

<sup>1</sup> http://ftp.arl.army.mil/ftp/historic-computers

Figure 1.7. A photograph of ENIAC

Because of the difficulties in the calculation part of the work, the processes were executed in series by operators working on a single binary element.

Being very energy-intensive, bulky and unreliable, these machines had an extremely crude programming language, known as machine language. Program development represents a considerable amount of work. Only one copy of each of these machines was made, and they were essentially used for research purposes. This was the case with the ENIAC, for example, which was involved in the research program for developing the Bomba [LAU 83], a machine used for decrypting messages during World War II.

#### 1.1.3.2. Second generation ( $\approx$ 1953–1963)

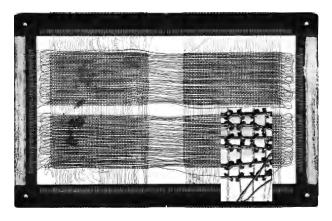

The second generation saw the advent of machines that were easier to operate (the IBM-701, among others). Transistors (the first of which dates back to 1947) started to replacing vacuum tubes. Memory used ferrite toroids, and operating systems, the first tools designed to facilitate the use of computers, were created. Until then, machines were not equipped with development environments or with a user interface as we know them now. Pre-programmed input-output modules, known as Input Output Control Systems (IOCS) are the only available tools to facilitate programming. Each task (editing, processing, etc.) is executed automatically. In order to save time between the end of a job and the beginning of another, the batch processing system is introduced, which groups together jobs of the same type. At the end of each task, the operating system takes control again, and launches the next job. Complex programming languages were created, and become known as symbolic coding systems. The first FORTRAN (FORmula TRANslator) compiler dates back to 1957 and is included with the IBM-704. The first specifications for COBOL (COmmon Business Oriented Language) were laid out in 1959 under the name COBOL 60. Large size applications in the field of management are developed. Magnetic tapes are used for archiving data.

#### 1.1.3.3. *Third generation* ( $\approx$ 1964–1975)

The PLANAR process, developed at FAIRCHILD starting in 1959, makes it possible to produce integrated circuits. This fabrication technique is a qualitative breakthrough: reliability, energy consumption and size being dramatically improved.

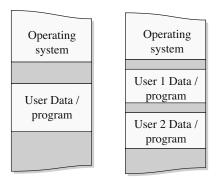

Alongside the advances in hardware performance came the concept of multiprogramming, the objective of which is to optimize the use of the machine. Several programs are stored in the memory at the same time, making it possible to quickly switch from one program to another. The concept of input-output device independence emerges. The programmer no longer has to explicitly specify the unit where the input-output operation is being executed. Operating systems are now written in high-level languages.

Several computer operating modes are created in addition to batch processing:

- Time sharing, TS, lets the user work interactively with the machine. The best known TS system, Compatible Time Sharing System (TSS), was developed at Massachusetts Institute of Technology (MIT) and led to the Multics system, developed collaboratively by MIT, Bell Labs and General Electric.

- Real time is used for industrial process control. Its defining feature is that the system must meet deadlines set by outside stimuli.

- Transaction processing is mainly used in management computing. The user communicates with the machine using a set of requests sent from a workstation.

The concept of *virtual memory* is developed. The joint use of drives and memory, which is seamless for the user, creates the impression of having a memory capacity far greater than what is physically available. The mid-1960s see the advent of the IBM-360 calculator series, designed for general use, and equipped with an operating system (OS/360) capable of managing several types of jobs (batch processing, time sharing, multiprocessing, etc.).

This new era sets the stage for a spectacular increase in the complexity of operating systems. Along with this series of calculators emerges the concept of compatibility between machines. This means that users can acquire a more powerful machine within the series offered by the manufacturer, and still hold on to their initial software investment.

The first multiprocessor systems (computers equipped with several "automaton-calculation" units) are born at the end of the 1960s. The development of systems for machines to communicate with one another leads to computer networks.

Figure 1.8. In the 1970s, memory still relied on magnetic cores. This photograph shows a  $4 \times (32 \times 64)$  bit plane. Each toroid,  $\approx 0.6$  mm in diameter, has three wires going through its center

Figure 1.9. The memory plane photographed here comprises twenty 512-bit planes. The toroids have become difficult to discern with the naked eye

In the early 1970s, the manufacturing company IBM adopted a new policy (unbundling) regarding the distribution of its products, where hardware and software are separated. It then becomes possible to obtain IBM-compatible hardware and software developed by companies in the service industry. This policy led to the rise of a powerful software industry that was independent of machine manufacturers.

#### 1.1.3.4. Fourth generation ( $\approx$ 1975–)

This fourth generation is tied to the systematic use of circuits with large, and later very large, scale integration (LLSI and VLSI). This is not due to any particular technological breakthrough, but rather due to the dramatic improvement in fabrication processes and circuit design, which are now computer assisted.

The integration of the different processor modules culminated in the early 1970s, with the development of the microprocessor. Intel® releases the I4004. The processor

#### 12 Computer Architecture

takes up only a few square millimeters of silicon surface. The circuit is called a *chip*. The first microcomputer, built around the Intel<sup>®</sup> I8080 microprocessor, came into existence in 1971.

**Figure 1.10.** A few reprogrammable memory circuits: from 8 kbits ( $\approx$ 1977) (right-hand chip) to 1 Mbit ( $\approx$ 1997) (left-hand chip) with no significant change in silicon surface area

**Figure 1.11.** A few old microprocessors: (a) Motorola<sup>™</sup> 6800 (1974, ≈6,800 transitors), Intel<sup>™</sup> 18088 (1979, ≈29,000), Zilog<sup>™</sup> Z80 (1976, ≈8,500), AMD Athlon 64X2 (1999, from ≈122 millions to ≈243 millions); (b) Intel i486 DX2 (1989, ≈1.2 million), Texas Instruments<sup>™</sup> TMX320C40 (1991, ≈650,000)

The increase in the scale of integration makes it possible for anybody to have access to machines with capabilities equivalent to the massive machines from the early 1970s. At the same time, the field of software development is exploding.

Designers rely more and more on parallelism in their machine architecture in order to improve performance without having to implement new technologies (pipeline, vectorization, caches, etc.). New architectures are developed: language machines, multiprocessor machines, and data flow machines.

Operating systems feature network communication abilities, access to databases and distributed computing. At the same time, and under pressure from microcomputer users, the idea that systems should be user friendly begins to take hold. The ease of use and a pleasant feel become decisive factors in the choice of software.

The concept of the virtual machine is widespread. The user no longer needs to know the details of how a machine operates. They are addressing a virtual machine, supported by an operating system hosting other operating systems.

The "digital" world keeps growing, taking over every sector, from the most technical-instrumentation, process command, etc.-to the most mundane-electronic payments, home automation, etc.

#### 1.2. Introduction to internal operation

#### 1.2.1. Communicating with the machine

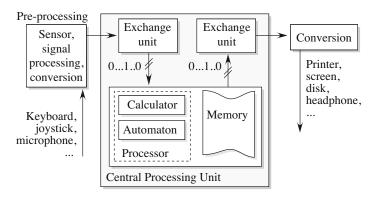

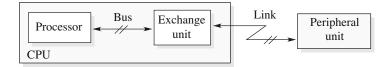

The three internal functioning units – the automaton, the calculation unit and the memory unit that contain the intermediate results and the program - appear as a single module accessible to the user only through the means of communication called peripheral units, or peripherals.

The data available as machine inputs (or outputs) are only rarely represented in binary. It can exist in many different formats: as text, an image, speech, etc. Between these sources of data and the three functional units, the following must be present:

- sensors providing an electrical image of the source;

- preprocessing hardware that, based on this image, provides a signal usable by the computer by meeting the electrical specifications of the connection (e.g. a filter, followed by a sampling of the source signal, itself followed by a link in series with the computer);

- exchange units located between the hardware and the computer's core.

Exchange units are a part of the computing machine. The user ignores their existence.

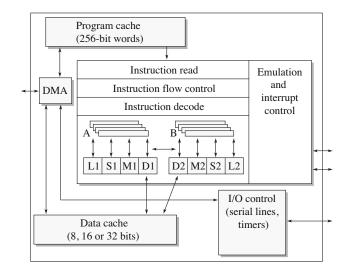

We will adopt the convention of referring to the system consisting of the processor (calculator and automaton) + memory + exchange units as the Central Processing Unit (CPU).

#### 14 Computer Architecture

Figure 1.12. User-machine communication

It is important to note that the symbols "0" and "1" used in Figure 1.12 to represent data are notations used by convention. This facilitates the representation of *logic* values provided by the computing machine. They could have been defined as " $\alpha$ " and " $\beta$ ", " $\phi$ " and "E", etc.

What emerges from this is a modular structure, the elements of which are the *processor* (calculation and automaton part), the *memory*, the *exchange units*, and connections, or *buses*, the purpose of which is to connect all of these modules together.

#### 1.2.2. Carrying out the instructions

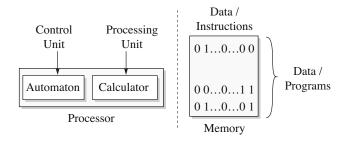

The functional units in charge of carrying out a program are the *automaton* and the *calculator*:

- the automaton, or *control unit*, is in command of all the operations;

- the module tasked with the calculation part will be referred as the *processing unit*.

Together, these two modules make up the *processor*, the "intelligent" part of the machine.

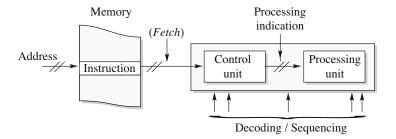

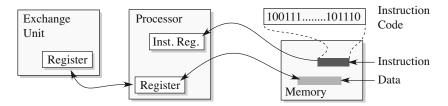

The basic operations performed by the computer are known as *instructions*. A set of instructions used for achieving a task will be referred to as a *program* (Figure 1.13).

Every action carried out by the computing machine corresponds to the execution of a program.

Figure 1.13. Processor and memory

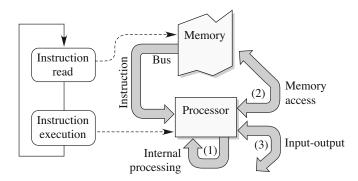

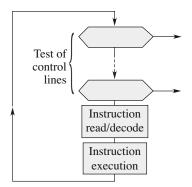

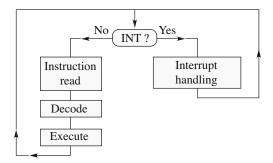

Once it has been turned on, the computer executes a "fetch-execution" cycle, which can only be interrupted by cutting its power supply.

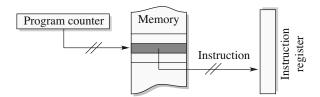

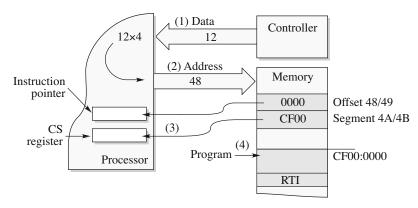

The fetch operation consists of retrieving within the memory an instruction that the control unit recognizes - decodes - and which will be executed by the processing unit. The execution leads to (see Figure 1.14) (1) a local processing operation, (2) something being read from or written into memory, or (3) something being read from or written into an exchange unit. The control unit generates all of the signals involved in going through the cycle.

Figure 1.14. Accessing an instruction

#### 1.3. Future prospects

Silicon will remain the material of choice of integrated circuit founders for many years to come. CMOS technology, the abbreviated form for complementary metal-oxide semiconductor (and its derivatives), long ago replaced TTL (transistor-transistor Logic) and ECL (emitter-coupled logic) technologies, even inside mainframes, because of its low consumption and its performance capabilities. The power supply voltage keeps dropping – 3.3, 2.9, 1.8 V are now common – while the scale of integration increases with improvements in etching techniques (half-pitch below 30 nm) and the use of copper for metallization. There are many improvements in fabrication processes. *Computer-aided design* (CAD), helps reduce development time and increases circuit complexity. The integration of test methods as early as during the design phase is an advantage for improving fabrication yields.

- It is the architecture that is expected to greatly enhance the machine performance. Parallelism is the main way to achieve this. It can be implemented at the level of the processor itself (operator parallelism and data parallelism) or on the higher level of the machine, by installing several processors which may or may not be able to cooperate. The improvement of the communication links becomes significant to transmit data. Protocols and bus technology are rapidly evolving to meet this objective.

- User-friendly interfaces are now commonplace. Multi-task operating systems are used on personal machines. Operating systems now have the ability to use the machine's hardware resources.

- The cost of a machine also includes the cost of the software designed for operating it. Despite the emergence of improved software technology (object-oriented approach, etc.), applications are developed and maintained with lifecycles far beyond the replacement cycle of hardware.

- As early on as the design phase, machines are equipped with the means of communication which facilitate their integration into *networks*. Working on a machine does not imply that the processing is performed locally. Similarly, the data handled can originate from remote sites. While this concept of delocalization is not new, the concept that access should be transparent is quite recent (*distributed* computing).

Throughout this book, the word *architecture* will refer to the organization of the modules which comprise the computing machine, to their interconnections, and not to how they are actually created using logic components: gates, flip-flops, registers or other, more complex elements.

## Chapter 2

## The Basic Modules

This chapter presents the main modules that constitute a computer: the memory, the processor and the exchange units. We will review the operation of registers and counters used in the execution of instructions. We will not discuss in detail the internal workings of the different modules, and will instead focus on their functions.

#### 2.1. Memory

Memory contains all of the data used by the processor. There are two types of data: a series of instructions and data on which to execute these instructions.

The information stored in a memory has no inherent significance. It only becomes meaningful once it is used. If it is handled by a program, it consists of *data*, and if it is read by the control unit to be executed, it consists of *instructions*.

For example, if we "double-click" on the icon of a word processor, then this program, stored on a drive, is transferred to memory using a program called a *loader*, which sees it as "data", until it becomes a "program" to the user.

#### 2.1.1. Definitions

Memory is a juxtaposition of *cells* called *memory words*, made up of m electronic elements that can exist in two stable states (the *flip-flop* logic function) referred to as

"0" and "1". Each cell can therefore code  $2^m$  different elements of information. Each of the m elements will be called a bit, abbreviated form for  $binary\ digit$ . If a memory word contains m bits, these are usually numbered from 0 to m-1, from the  $least\ significant\ bit\ (LSB)$ , to the  $most\ significant\ bit\ (MSB)$ .

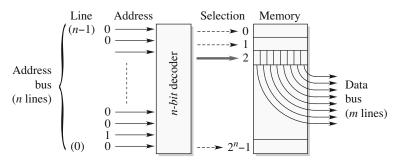

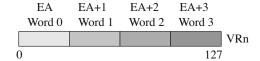

Each cell is uniquely identified by a number – its *address*. The information in the memory is accessed by setting the n lines of the address buses. The binary configuration of these n lines codes the address of the word, whose m bits of content can then be read by the data bus. This is achieved using a  $n \to 2^n$  decoder located between the address bus and the actual memory, so that the values of the addresses scale from 0 to  $2^n - 1$ .

In Figure 2.1, the configuration  $\{00\ldots0010\}$  leads to the selection of the memory word with the address 2, the content of which becomes accessible to the data bus.

Figure 2.1. Memory

The delay between the setting of the address and the time when the data becomes available on the data bus is called the *access time*. The information stored in a cell is called the *content* of the address:

- a memory cell is denoted by M, where M is the cell's address;

- the content of the memory word with address M is denoted by [M].

The name used for these memory words depends on their length. While a *byte* always refers to an eight-bit cell, the same is not true for a *word*, which can consist of 16 bits, 32 bits, etc. A 32-bit word is sometimes called a *quadlet*, and a half-byte is a *nibble* or *nybble*.

When each byte has an address, the memory is said to be *byte addressable* and each of the bytes in a 32-bit memory word can be accessed individually. The addresses of words are multiples of four.

The unit of memory size is generally a byte, in which case it is expressed in kilobytes (kB), megabytes (MB) or gigabytes (GB), with:

```

1 \text{ kilobyte} = 2^{10} \text{ bytes} = 1,024 \text{ bytes},

1 megabyte = 2^{20} bytes = 1,048,576 bytes,

1 gigabyte = 2^{30} bytes = 1,073,741,824 bytes.

```

#### 2.1.2. A few elements of technology

#### 2.1.2.1. Concept

Memory design relies on any of the following three technologies:

- Each basic element consists of a flip-flop: this technique is implemented to produce what is known as volatile and static memories: volatile because once the power supply is shut down, the information is lost, and static because the information is stable as long as the power supply is maintained.

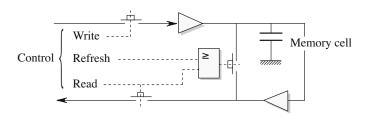

- The basic element is comparable to a capacitor, which can be either charged or not charged: this concept applies to volatile and dynamic memories (Figure 2.2). The term dynamic means that the information is lost whenever the capacitor discharges.

Figure 2.2. Concept of the dynamic memory cell: the content of the cell must periodically be refreshed, something which is also achieved when the element is read

This type of memory must periodically be refreshed, a task which can be accomplished using a read or write cycle.

- Producing the cell requires a phenomenon similar to the "breakdown" of a diode: this is how the so-called *non-volatile* memory is made. Once the content has been programmed, it exists permanently regardless of whether the power is on or off.

Volatile memories are usually known as RAM (Random Access Memory) and non-volatile memories as ROM (Read-Only Memory). Depending on the techniques, other terms such as DRAM (Dynamic RAM), PROM (Programmable ROM), F-PROM (Field-Programmable ROM), REPROM (REProgrammable ROM) and EAROM (Electrically Alterable ROM), are sometimes used.

#### 2.1.2.2. Characteristics

The following are the main characteristics of memory:

- The access time, i.e. the time it takes from the moment an address is applied to the moment when we can be certain that the retrieved data is *valid*. This time is measured in nanoseconds (1 nanosecond =  $10^{-9}$  s), generally in the range of 1 to 100 ns. This parameter is not sufficient for measuring the machine's "memory performance". With modern computers, a memory access can sometimes be performed according to a complex protocol, and it is difficult to determine a value that is independent of the machine's architecture.

- The *size*, expressed in thousands, millions, or billions of bytes. Currently, the most common sizes are above 4 GB for personal computers, tens of GB for servers, and greater still for large machines (*supercomputers*).

- The *technology* which falls into two categories:

- rapid memories that rely on transistor-transistor logic (TTL) technology;

- Complementary MOS (CMOS) technologies, which have very low energy consumption and allow for high-scale integration (personal computers on the market today have memory components equipped with several billion bytes).

- The *internal organization* which allows more or less rapid access to information. Examples of available memory include VRAM (*Video RAM*), EDO (*Extended Data Out*), *synchronous RAM*, etc.

#### 2.2. The processor

#### 2.2.1. Functional units

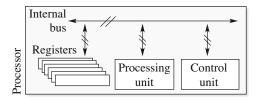

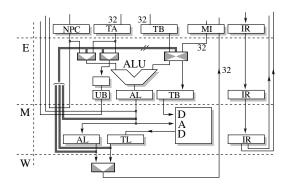

The processor houses two functional units: the *control unit* and the *processing unit* (see Figure 2.3).

Figure 2.3. Execution of an instruction

#### 2.2.1.1. The control unit

The control unit has three functions (see Figure 2.3):

- It fetches instruction stored in the memory: it sets the address of the instruction on the address bus, then, after a delay long enough to ensure that the address is in fact stable on the data bus (or the instruction bus, for machines equipped with distinct buses), it loads the instruction it has just obtained into a register.

- It decodes the instruction.

- It indicates to the processing unit which arithmetic and logic processes need to be performed, and generates all of the signals necessary to the execution of the instruction. This is the execution step.

#### 2.2.1.2. The processing unit

The processing unit ensures the execution of elementary operations "specified" by the control unit ("processing indications"). The information handled and the intermediate results are stored in memorization elements internal to the processor, known as registers.

No operation is made directly with the memory cells: they are instead copied into registers, which may or may not be accessible to the programmer, before being processed.

The control unit, the processing unit and the registers are connected to each other, which makes it possible to load or read in parallel all of their bits. These communication lines are known as internal buses (Figure 2.4).

Figure 2.4. Internal bus

#### 2.2.2. Processor registers

#### 2.2.2.1. Working register

Working registers are used to store results without accessing the memory. This simplifies the handling of data (there is no need for managing addresses) and the time

#### 22 Computer Architecture

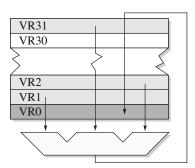

it takes to access the information is shorter. In most classic architecture processors, the number of registers is in the order of 8 to 32.

#### 2.2.2.2. Accumulator register

In many classic architecture machines, the set of instructions favors certain registers known as *accumulator registers* or simply *accumulators*. In Intel<sup>®</sup> x86 series microprocessors, for example, all of the instructions for transfers between memory and registers, or between registers, can affect the accumulator register, denoted by AX. The same is not true for registers indexed SI or DI, which offer more limited possibilities for handling information.

#### 2.2.2.3. Stack pointer

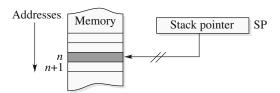

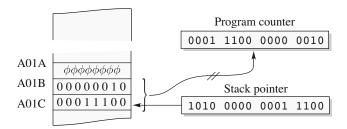

*Stack pointers* are mainly used in the mechanism for calling functions or subroutines. The stack is a part of the memory which is managed (Figure 2.5) according to the content of the *stack pointer* register.

Figure 2.5. The stack

The stack pointer provides the address of a memory word called the *top of the stack*. The top of the stack usually has the same address as the word in the stack with the smallest address n.

The stack pointer and the stack are also handled by special instructions or during autosaves of the processor state (calls and returns from subroutines, interrupts, etc.).

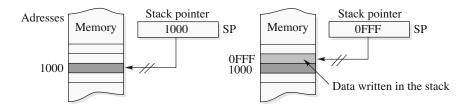

EXAMPLE 2.1. — Let us assume that in an initial situation (Figure 2.6), a stack pointer contains the value  $1{,}000_{16}$ , which is the address of the memory word at the top of the stack. The stacking is done on a single memory word. The stack pointer is *decremented* and the information is stored at the top of the stack, in this case at the address  $0 FFF_{16}$  (Figure 2.6).

In certain machines, the stack is created using rapid memory distinct from the main memory (the memory containing data and programs). This is known as a *hardware stack*.

Figure 2.6. Writing in the stack

#### 2.2.2.4. Flag register

The flag register, or condition code register, plays a role that becomes clear when performing a sum with a carry. When summing two integers coded in several memory words, the operation must be performed over several summing instructions, each instruction involving only a word. While there is no need to consider a carry for the first sum, since it involves the least significant bits of the operands, the same cannot be said of the following sums. The carry resulting from the execution of a sum is stored in the flag register. Its role is to memorize the information related to the execution of certain instructions, such as arithmetic instructions and logic instructions.

#### REMARKS 2.1.-

- Flags are used by conditional branching instructions, among others.

- Not all instructions lead to flag modifications. In Intel® x86 series microprocessors, assignment instructions (transfers from register to register, or between memory and a register) do not affect flags.

- The minimum set of flags is as follows:

- the *carry* flag C or CY;

- the zero flag Z, which indicates that an arithmetic or logic operation has produced a result equal to zero, or that a comparison instruction has produced an equality;

- the parity flag P, which indicates the parity of the number of 1 bit in the result of an operation;

- the sign flag, or negative flag S, which is nothing but a copy of the most significant bit in the result of the instruction that has just been executed;

- the overflow flag V, an indicator which can be used after executing operations on integers coded in two's complement (see Remark 2.2).

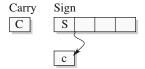

REMARK 2.2.— If we perform sums on numbers using the two's complement binary representation, it is important to avoid any error due to a carry which would propagate to the sign bit and change it to an erroneous value. Consider, for example, numbers coded in four bits in two's complement. Let C and S be the carry and sign flags, respectively, and let c be the carry generated by the sum of the three least significant bits (Figure 2.7).

Figure 2.7. Sign and carry

Let us examine each possible case in turn, starting with the case of two positive numbers A and B.

1) Let the values of the operands be 3 and 5:

$$\begin{array}{ll} A & = 0\ 0\ 1\ 1 \to +3 \\ B & = 0\ 1\ 0\ 1 \to +5 \\ A + B = 1\ 0\ 0\ 0 \to -8 \end{array}$$

The result obtained is wrong. Note that c takes on the value 1, while C and S take on the values 0 and 1, respectively. In the case where we get the right result, for example with A=2 and B=3, then c, C and S take on the value 0.

2) In the case of two negative numbers:

$$\begin{array}{lll} A & = & 1\ 0\ 1\ 0 \to -6 \\ B & = & 1\ 0\ 1\ 1 \to -5 \\ A + B = 1\ 0\ 1\ 0\ 1 \to +5 \end{array}$$

For these values of A and B that lead to an erroneous result, note that c, C and S take on the values 0, 1, and 0, respectively. When we get the right result, the values of c, C and S become 1, 1 and 1, respectively.

3) For numbers of opposite signs, we find that no error occurs:

$$A = 0110 \rightarrow +6$$

$B = 1011 \rightarrow -5$

$A + B = 10001 \rightarrow +1$

We can sum up the results of all possible cases by drawing up a Karnaugh map where overflows are represented by the number 1. The flag indicating these cases is denoted by OV:

|              | 00     | 01 | 11     | 10 | CS |

|--------------|--------|----|--------|----|----|

| 0            | 0      | 0  | $\phi$ | 1  |    |

| 1            | $\phi$ | 1  | 0      | 0  |    |

| $\mathbf{c}$ |        |    |        |    | OV |

The overflow bit OV is then equal to  $C \otimes c = \overline{C} c + \overline{c} C$ .

REMARK 2.3.- There is a flag, known as the half carry flag, which is usually not directly useable by the programmer. It is used for the propagation of the carry when working with BCD coded numbers (see Chapter 3). Consider the sum of the two numbers  $18_{10}$  and  $35_{10}$  coded in BCD (each decimal figure is converted to four-digit binary):

| Base 10 | BCD code  |

|---------|-----------|

| 18      | 0001 1000 |

| +35     | 0011 0101 |

| = 53    | 0101 0011 |

Since the adder works in two's complement, it produces the result 0100 1101. The intermediate carry, or half carry, indicates that the result of summing the least significant digits is >9. It is used internally when it is preferable to have a result also coded in BCD using decimal adjust instructions. In the Intel® x86 processor, for example, the sum of the two previous 8 bits, BCD coded integers can be performed as follows (al and bh are 8-bit registers):

```

; al contains 18 (BCD) i.e. 0001 1000

; bh contains 35 (BCD) i.e. 0011 0101

add al,bh ; al + bh --> al : 18 + 35 --> 4D

daa ; decimal adjust of al: 4D --> 53

```

#### 2.2.2.5. Address registers

Registers can sometimes be involved in memory addresses. The relevant registers can be either working registers or specialized registers, with the set of instructions defining the role of each resister. Some examples of these registers are:

- *indirection* registers, the content of which can be considered addresses;

- index registers, which act as an offset in the address calculation, specifically a value added to the address;

- base registers, which provide an address in the calculation of an address by indexing (the address of the operand is obtained by summing the contents of the base and index registers);

- segment registers (see Chapter 7), limit registers, etc.

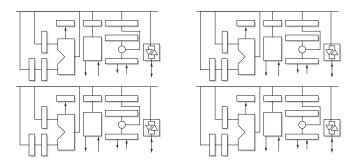

### 2.2.3. The elements of the processing unit

The *processing unit* is the component tasked with executing arithmetic and logic operations, under the command of the control unit. The core of the processing unit is the *arithmetic and logic unit* (ALU). The ALU consists of a combinational logic circuit which performs elementary operations on the content of the registers: sums, subtractions, OR, AND, XOR, complement, etc.

### 2.2.3.1. Arithmetic operations

The sum/subtraction operators are achieved on a cellular level using "bit-by-bit" adders. The problem with designing fast adders comes from the propagation speed of the carry throughout all of the adder stages. A solution ([GOS 80]) consists of "cutting up" the n-n adder into several p-p adder blocks, so that it becomes possible to propagate the carry from a p-p block to another p-p block. The carry is calculated on a global level for each p-p adder. This is known as a *look ahead carry*. Another technique consists, for this same division into p-p adders, of propagating the carry throughout the p-p floor only if it is necessary (carry-skip adders).

Multiplication can also be achieved in a combinational fashion. The only obstacle is the surface occupied by such a multiplier, the complexity of which is of the order of  $n^2$  1–1 adders.

### 2.2.3.2. The ALU and its flags

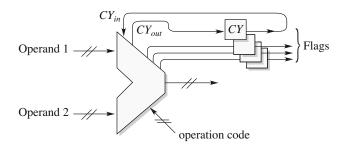

The processing unit is often defined as the set consisting of the ALU and a certain number of registers that are inseparable from it (including flag registers and accumulator registers).

The command lines define the operation that needs to be performed, including, both as input and as output of the ALU, two lines for the *carry*:

- $-CY_{in}$ , which originates from the output of the carry flip-flop;

- $-CY_{out}$  as input for the same flip-flop.

Other lines, referred to as *flags*, provide the state of the result of the operation: *overflow*, *zero*, etc.

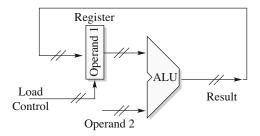

Figure 2.8. The arithmetic logic unit

REMARK 2.4.- Consider the case where a register is both the source and the destination of a sum. After executing the sum, the result should be located in the register. Consider the initial situation described in Figure 2.9.

Figure 2.9. Operational diagram

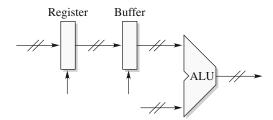

Once the instruction is executed, the result is loaded in the register under the command of the control unit. However, in order for the operation to work properly, the information present at the register input cannot be modified when the register is loaded. This is not the case in the operational diagram shown in Figure 2.9. A simple method for avoiding this pitfall consists of inserting what is known as a buffer register between the register and the ALU (Figure 2.10).

Figure 2.10. The buffer register

In the first step, the content of the register is transferred to the buffer, then, in the second step, the result is written into the register. We will encounter this scheme again in the example used for illustrating an instruction (Chapter 5). Later, we will consider the buffer–register system as a single register.

Any complex operation is performed using a combination of elementary operations available on the ALU and shift operations on registers. The multiplication operation, for example, will rely on sums and shifts if the specialized circuit used for its operation is not present in the ALU.

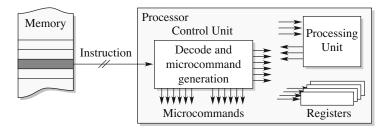

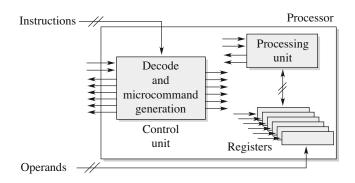

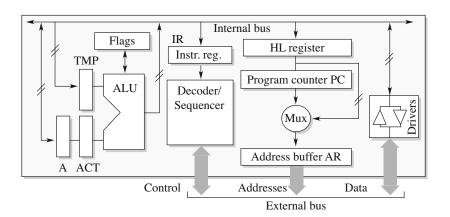

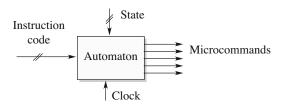

### 2.2.4. The elements of the control unit

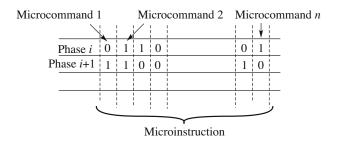

The control unit sends control signals (also called *microcommands*) to ensure the proper execution of the decoded instructions.

Figure 2.11. Control unit

The control unit consists of four modules:

- The *instruction register*, denoted by IR, receives the code for the instruction that the control unit has "fetched" from memory.

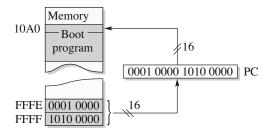

- The *program counter* (PC), or *instruction pointer* (IP), is a *programmable* counter containing the address of the instruction that needs to be executed. By "programmable", we mean that it is possible to modify its content at any time without following the counting sequence. This is the case, for example, any time the sequentiality rule is violated (branches, subroutine calls, etc.). The instruction whose address is provided by the content of the program counter is placed in the instruction register, so that it can be decoded (Figure 2.12).

A 16-bit program counter enables access to  $2^{16}$  program words. Given the Boolean nature of the information stored in memory (nothing looks more like an instruction than data), the content of the memory word is only an instruction if the program counter contains its address!

Figure 2.12. Accessing an instruction

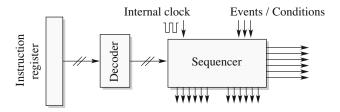

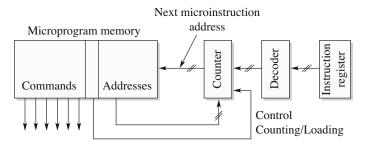

- The *instruction decoder* is a circuit for recognizing the instruction contained in the instruction register. It indicates to the sequencer the sequence of basic instructions (microcommand sequence) that need to be performed to execute the instruction.

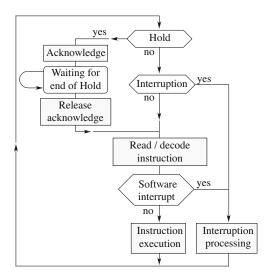

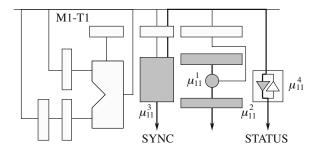

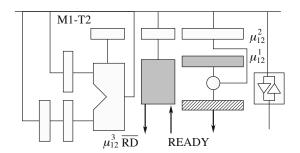

- The sequencer is the device that produces the sequence of commands, known as microcommands, used for loading, specifying the shift direction, or operations for the ALU, necessary for the execution of the instruction.

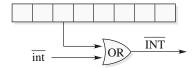

The sequencer's internal logic takes into account a certain number of events originating from the "outside", or generated by the exchange units or the memory: interrupts, holds, etc. The sequence of microcommands is delivered at a rate defined by the *internal clock* (Figure 2.13).

Figure 2.13. Decoder/sequencer

The speed of this clock determines the speed of the processor, and more generally, of the computer, if the elements surrounding the processor can keep up the pace. The phrase "1.2 GHz microcomputer" indicates that the basic clock frequency is 1.2 GHz. This specification is an indication of the performance of the processor, not of the machine.

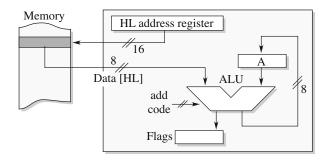

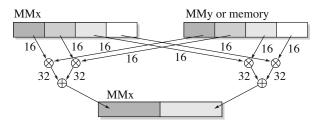

### 2.2.5. The address calculation unit

Calculating addresses requires an arithmetic unit. The calculation can be performed by the ALU, as was the case in certain first generation microprocessors. This method has the advantage of reducing the number of components in the central processing unit. On the other hand, the additional register operations and the resulting exchanges end up being detrimental to the machine's performance. The calculation of addresses is more often performed by an arithmetic unit specific to the task.

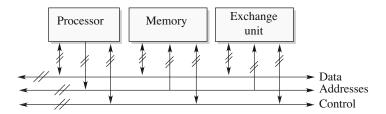

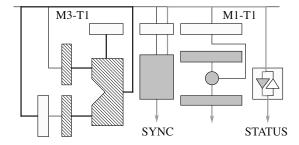

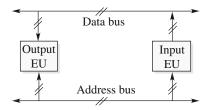

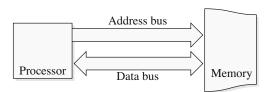

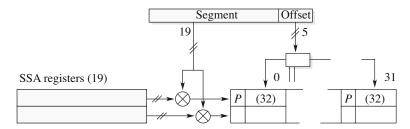

### 2.3. Communication between modules

The processor is physically connected to the memory and the exchange units by a set of lines. These connections form the so-called *external bus*, not to be confused with the *internal bus* connecting the ALU, the registers, etc. In the case of typical processors, the external bus consists of a data bus, an address bus, and a control bus.

The number of wires of the data bus gives us the number of bits that can be transferred to the memory in one access cycle. The transfer speed is called the bus *bandwidth*, usually given in bytes per second. This bandwidth depends to a large extent on the electrical characteristics, on the method used for performing transfers (synchronous and asynchronous modes), and on the bus exchange protocol.

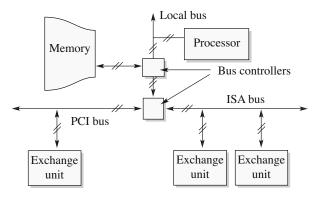

PC-type microcomputers have a main bus (*Peripherals Component Interconnect*, PCI) for exchanges with the memory and modern peripheral cards. They are also equipped with dedicated buses, in particular the bus dedicated to transfers to the video memory (*Accelerated Graphics Port*, AGP).

**Figure 2.14.** Local data bus and external data bus: the connection between the local bus and the PCI bus depends on the generation of the machine, on the type of PCI bus used (PCI or PCI Express), and on the presence of northbridge and southbridge bus controllers

So far, we have only discussed the transfer of information from the data bus. No such transfer can occur without first gaining access to this information. That is the role of the address bus. The processor provides this bus with the addresses of the elements it wants access to. The width, that is the number of lines, of the address bus determines the addressable memory space.

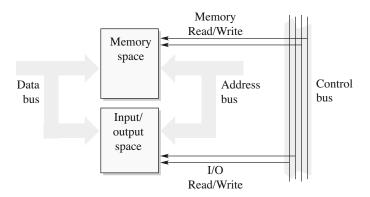

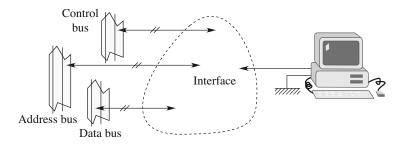

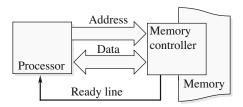

Other lines are necessary for the whole system to work properly, for example a read/write indicator, or lines indicating the state of the exchange units. The set of lines conveying this information is referred to as the control bus, or command bus (Figure 2.15).

The system comprising the data, address, and control buses constitutes what is called the external bus

Figure 2.15. Address, data and control buses

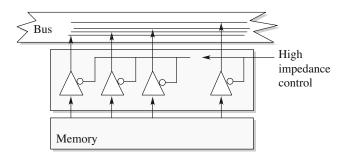

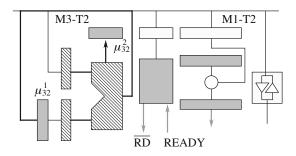

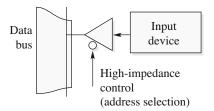

In an effort to limit the number of communication lines (the sum of the bus widths, the number of electrical supply lines, and the clock signals), the solution that was chosen is to multiplex these bus lines, meaning that the same physical lines are used as both address and data lines.

On this external bus, it is possible to connect several processors or exchange units likely to take control of the buses - multiprocessor systems or direct memory access devices (section 6.3.2). When an exchange unit controls the buses, the other units have to be protected. This is done with the help of three-state drivers, which can exist in three states: 0, 1 and high impedance. This last state is equivalent to a physical disconnection of the line (Figure 2.16).

### 2.3.1. The PCI bus

The PCI bus is used in a very broad sense as an intermediate bus between the processor bus - the local bus - and the input-output buses [ABB 04]. It has been available in different versions – 32 or 64 bits, various information signaling voltages, supported bandwidths, etc. – since 1992, the year of its inception by Intel<sup>®</sup>.

Figure 2.16. Three-state drivers

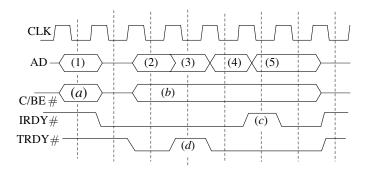

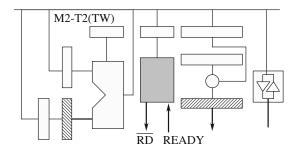

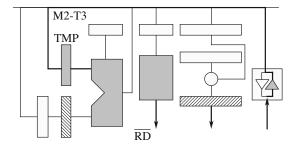

The PCI bus conveys data between the processor and the memory and any input—output devices by taking into account the presence of caches and the fact that they need to be updated (Chapter 8.) A bus is dedicated to the transfer of addresses and data (AD bus), whereas a control bus (C/BE# bus) indicates the phase of the bus. Figure 2.17 describes a read transfer between the processor and the memory. This diagram is very simplified, since not all of the signals involved in the communication protocol are shown.

**Figure 2.17.** Example of a read operation on a PCI bus: on the C/BE# bus, the memory read command is generated (a) and the address is sent (1) over the AD bus. IRDY# indicates that the processor (the initiator) is ready to receive the data sent by the memory (the target) in (2), (4), and (5) under the command of the C/BE# bus (b). Cycle (3) is a wait state signaled by the switch of TRDY# to 1 in (d). The switch of IRDY# to 1 in (c) indicates the end of the transfer

A parity check system on the set of lines AD and C/BE# is implemented. The PAR line shows the parity "calculated" by the devices sending the information (address or data) and the SERR# and PERR# lines indicate a parity error provided by the target of the exchange and its source, respectively, if it happens to be necessary.

Each additional board is equipped with a software/hardware device (firmware), accessible in a particular addressing space (the PCI configuration space), which makes it possible to know if it is present when the machine starts, to know the type of resources (interrupts, memory and input-outputs) and to obtain a description of the memory space, or of the input-output space, which is available on the board.

### Chapter 3

# The Representation of Information

When representing data or communicating with the computer, the user relies on symbols – numbers, letters and punctuation – which together form *character strings*.

For example, the lines:

```

1 i = 15; r = 1.5;

2 car1 = "15"; car2 = "Hello";

3 DIR > Result.doc

4 cat Result.tex

```

are interpreted as the instructions for a program (lines 1 and 2) or as commands sent to the operating system (lines 3 and 4). This *external representation* of data is not directly understandable to the machine. It requires a translation (*coding*) into a format that the computer can use. We will refer to the result of this operation as an *internal representation*. It involves in every case the use of logic symbols denoted by 0 and 1 (section 3.2.2). For reasons of clarity, and/or ease of specification, *logical* data are most often divided into sets of eight elements called *bytes*.

In this chapter, we will distinguish the following types: numbers, integer or real, and characters.

Consider again the previous example: internal coding of the data "15" will be different depending on whether the data are stored in the i variable or the car1 variable. One is *numerical*, the other a *character string*. The external representation is the same for the two entities, despite the fact that they are fundamentally different in nature. The human operator is able differentiate them and can adapt their process

according to context or using their knowledge of the object. Machines, on the other hand, require different internal representations for objects of different types. In this chapter, we present the rules that make it possible to convert *external format*  $\rightarrow$  *internal format*, without making assumptions about the final implantation of the result in the machine's memory.

### 3.1. Review

### 3.1.1. Base 2

The *representation* of a number x in base b is defined as the vector  $\{a_n, \ldots, a_0, a_{-1}, \ldots, a_{-p}\}$  such that:

$$x = \sum_{i=-p}^{n} a_i b^i$$

[3.1]

where the  $a_i$  are integers between 0 and (b-1). The index i and the number  $b^i$  are the position and the weight, respectively, of the symbol  $a_i$ . The coefficients  $a_n$  and  $a_{-p}$  are the most significant and least significant digits, respectively. In the case of base 2 (binary coding), the coefficients  $a_i$  may assume the values 0 or 1 and will be referred to as bits, shorten form for binary digit.

### EXAMPLE 3.1.-

- The binary number  $1010 = 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 0 = 10_{10}$ .

- The change from base 10 to base 2 is done by a *series of divisions* by 2 for the integer part and a *series of multiplications* by 2 for the fractional part. Consider the number 20.375 in base 10.

We can switch to its base 2 representation by doing the following:

1) For the integer part,  $x_{INT}$ , we perform the series of divisions:

The result is given by the last quotient and the previous remainders. We get  $x_{\rm INT}=10100_2.$

2) The fractional part  $x_{FRAC}$  is obtained by a series of multiplications by 2. Thus, for 0.375:

$$0.375 \times 2 = \underline{0}.75$$

$0.75 \times 2 = \underline{1}.5$

$0.5 \times 2 = 1$

The digits of the fractional part are given by the integer parts of results of the multiplications by 2. Here, we get  $x_{\rm FRAC}=0.011_2$ . In the end,  $20.375_{10}=x_{\rm INT}+$  $x_{\rm FRAC} = 10100.011_2$ . Note that the base 2 representation is not necessarily finite, even if the base 10 representation is. Thus,  $0.2_{10}$  will give us 0.001100110011...The number of digits in the fractional part is infinite.

The error introduced by limiting the number of bits of the representation is known as the truncation error. The error from rounding up or down in this representation is the rounding error.

For example,  $0.2_{10} \approx 0.0011001100$  by truncation and  $0.2_{10} \approx 0.0011001101$  by rounding.

### 3.1.2. Binary, octal and hexadecimal representations

In the binary case, which is of particular interest to us, the two logic states used for the representation of data are symbolized by 0 and 1, whether the data are numerical or not. For practical reasons, the external representation often uses base 8 (octal representation) or 16 (hexadecimal representation).

The octal system uses eight symbols: 0, 1, 2, 3, 4, 5, 6, 7. Changing from base 2 to base  $8 = 2^3$  is done instantly by dividing the binary digits into sets of three, "starting from the decimal point". For example:

$$1011101.01101_2 = 1 \mid 011 \mid 101.011 \mid 010 = 135.32_8$$

Base 16 uses the symbols 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F. Changing from base 2 to base  $16 (= 2^4)$  is done the same way, by dividing the binary digits into sets of four, "starting from the decimal point". For example:

$$1011101.01101_2 = 101 \mid 1101.0110 \mid 10 = 5D.68_{16}$$

These bases not only give us a condensed representation of binary digits, but also make it possible to instantly convert to base 2.

### 3.2. Number representation conventions