# Programming Language Syntax

#### 2.3.4 Syntax Errors

#### EXAMPLE 2.43 Syntax error in C (reprise)

The main text illustrated the problem of syntax error recovery with a simple example in C:

A = B : C + D;

The compiler will detect a syntax error immediately after the B, but it cannot give up at that point: it needs to keep looking for errors in the remainder of the program. To permit this, we must modify the input program, the state of the parser, or both, in a way that allows parsing to continue, hopefully without announcing a significant number of spurious cascading errors and without missing a significant number of real errors. The techniques discussed below allow the compiler to search for further syntax errors. In Chapter 4 we will consider additional techniques that allow it to search for additional static semantic errors as well.

#### Panic Mode

Perhaps the simplest form of syntax error recovery is a technique known as *panic mode*. It defines a small set of "safe symbols" that delimit clean points in the input. When an error occurs, a panic mode recovery algorithm deletes input tokens until it finds a safe symbol, then backs the parser out to a context in which that symbol might appear. In the earlier example, a recursive descent parser with panic mode recovery might delete input tokens until it finds the semicolon, return from all subroutines called from within stmt, and restart the body of stmt itself.

Unfortunately, panic mode tends to be a bit drastic. By limiting itself to a static set of "safe" symbols at which to resume parsing, it admits the possibility of deleting a significant amount of input while looking for such a symbol. Worse, if some of the deleted tokens are "starter" symbols that begin large-scale constructs in the language (e.g., begin, procedure, while), we shall almost surely see spurious cascading errors when we reach the end of the construct.

Consider the following fragment of code in Modula-2:

The problem with panic mode

EXAMPLE 2.44

```

IF a b THEN x;

ELSE y;

END;

```

When it discovers the error at b in the first line, a panic-mode recovery algorithm is likely to skip forward to the semicolon, thereby missing the THEN. When the parser finds the ELSE on line 2 it will produce a spurious error message. When it finds the END on line 3 it will think it has reached the end of the enclosing structure (e.g., the whole subroutine), and will probably generate additional cascading errors on subsequent lines. Panic mode tends to work acceptably only in relatively "unstructured" languages, such as Basic and (early) Fortran, which don't have many "starter" symbols.

#### **Phrase-Level Recovery**

We can improve the quality of recovery by employing different sets of "safe" symbols in different contexts. Parsers that incorporate this improvement are said to implement *phrase-level recovery*. When it discovers an error in an expression, for example, a phrase-level recovery algorithm can delete input tokens until it reaches something that is likely to follow an expression. This more local recovery is better than always backing out to the end of the current statement, because it gives us the opportunity to examine the parts of the statement that follow the erroneous expression.

Niklaus Wirth, the inventor of Pascal, published an elegant implementation of phrase-level recovery for recursive descent parsers in 1976 [Wir76, Sec. 5.9]. The simplest version of his algorithm depends on the FIRST and FOLLOW sets defined at the end of Section 2.3.1. If the parsing routine for nonterminal *foo* discovers an error at the beginning of its code, it deletes incoming tokens until it finds a member of FIRST(*foo*), in which case it proceeds, or a member of FOLLOW(*foo*), in which case it returns:

```

procedure foo

if (input_token \notin FIRST(foo)) and (not EPS(foo))

report_error -- print message for the user

repeat

delete_token

until input_token \in (FIRST(foo) \cup FOLLOW(foo) \cup {$$})

case input_token of

...:...

...:...

otherwise return -- error or foo \longrightarrow \epsilon

```

Note that the report\_error routine does *not* terminate the parse; it simply prints a message and returns. To complete the algorithm, the match routine must be

EXAMPLE 2.45

Phrase-level recovery in recursive descent

altered so that it, too, will return after announcing an error, effectively inserting the expected token when something else appears:

```

procedure match(expected)

if input_token = expected

consume input_token

else

report_error

```

Finally, to simplify the code, the common prefix of the various nonterminal subroutines can be moved into an error-checking subroutine:

```

procedure check_for_error(symbol)

if (input_token ∉ FIRST(symbol)) and (not EPS(symbol))

report_error

repeat

delete_token

until input_token ∈ (FIRST(symbol) ∪ FOLLOW(symbol) ∪ {$$})

```

#### Context-Specific Look-Ahead

Though simple, the recovery algorithm just described has an unfortunate tendency, when  $foo \rightarrow \epsilon$ , to predict one or more epsilon productions when it should really announce an error right away. This weakness is known as the *immediate error detection* problem. It stems from the fact that FOLLOW(*foo*) is contextindependent: it contains all tokens that may follow *foo* somewhere in some valid program, but not necessarily in the current context in the current program. (This is basically the same observation that underlies the distinction between SLR and LALR parsers, as mentioned in Section 2.3.3 [page 91]).

As an example, consider the following incorrect code in our calculator language:

Y := (A \* X X \* X) + (B \* X \* X) + (C \* X) + D

To a human being, it is pretty clear that the programmer forgot a \* in the  $x^3$  term of a polynomial. The recovery algorithm isn't so smart. In a recursive descent parser it will see an identifier (X) coming up on the input when it is inside the following routines:

program stmt\_list stmt expr term factor expr term factor\_tail factor\_tail

example 2.46

Cascading syntax errors

Since an id can follow a *factor\_tail* in some programs (e.g.,  $A := B \ C := D$ ), the innermost parsing routine will predict *factor\_tail*  $\longrightarrow \epsilon$ , and simply return. At that point both the outer factor\_tail and the inner term will be at the end of their code, and they, too, will return. Next, the inner expr will call term\_tail, which will also predict an epsilon production, since an id can follow a term\_tail in certain programs. This will leave the inner expr at the end of its code, allowing it to return. Only then will we discover an error, when factor calls match, expecting to see a right parenthesis. Afterward there will be a host of cascading errors, as the input is transformed into

Y := (A \* X) X := X B := X\*X C := X

#### EXAMPLE 2.47

Reducing cascading errors with context-specific look-ahead

### EXAMPLE 2.48

Recursive descent with full phrase-level recovery

To avoid inappropriate epsilon predictions, Wirth introduced the notion of context-specific FOLLOW sets, passed into each nonterminal subroutine as an explicit parameter. In our example, we would pass id as part of the FOLLOW set for the initial, outer expr, which is called as part of the production  $stmt \rightarrow id := expr$ , but *not* into the second, inner expr, which is called as part of the production  $factor \rightarrow (expr)$ . The nested calls to term and factor\_tail will end up being called with a FOLLOW set whose only member is a right parenthesis. When the inner call to factor\_tail discovers that id is not in FIRST( $factor_tail$ ), it will delete tokens up to the right parenthesis before returning. The net result is a single error message, and a transformation of the input into

Y := (A \* X \* X) + (B \* X \* X) + (C \* X) + D

That's still not the "right" interpretation, but it's a lot better than it was.

The final version of Wirth's phrase-level recovery employs one additional heuristic: to avoid cascading errors it refrains from deleting members of a statically defined set of "starter" symbols (e.g., begin, procedure, (etc.). These are the symbols that tend to require matching tokens later in the program. If we see a starter symbol while deleting input, we give up on the attempt to delete the rest of the erroneous construct. We simply return, even though we know that the starter symbol will not be acceptable to the calling routine. With context-specific FOLLOW sets and starter symbols, phrase-level recovery looks like this:

```

procedure check_for_error(symbol, follow_set)

if (input_token ∉ FIRST(symbol)) and (not EPS(symbol))

report_error

repeat

delete_token

until input_token ∈ FIRST(symbol) ∪ follow_set ∪ starter_set ∪ {$$}

```

```

procedure expr(follow_set)

check_for_error(expr, follow_set)

case input_token of

...: ...

valid starting tokens

...: ...

otherwise return

```

#### **Exception-Based Recovery in Recursive Descent**

An attractive alternative to Wirth's technique relies on the exception-handling mechanisms available in many modern languages (we will discuss these mechanisms in detail in Section 8.5). Rather than implement recovery for every nonterminal in the language (a somewhat tedious task), the exception-based approach identifies a small set of contexts to which we back out in the event of an error. In many languages, we could obtain simple, but probably serviceable error recovery by backing out to the nearest statement or declaration. In the limit, if we choose a single place to "back out to," we have an implementation of panic-mode recovery.

The basic idea is to attach an exception handler (a special syntactic construct) to the blocks of code in which we want to implement recovery:

Code for declaration would be similar. For better-quality repair, we might add handlers around the bodies of expression, aggregate, or other complex constructs. To guarantee that we can always recover from an error, we must ensure that all parts of the grammar lie inside at least one handler.

When we detect an error (possibly nested many procedure calls deep), we *raise* a syntax error exception ("raise" is a built-in command in languages with exceptions). The language implementation then unwinds the stack to the most recent context in which we have an exception handler, which it executes in place of the remainder of the block to which the handler is attached. For phrase-level (or panic mode) recovery, the handler can delete input tokens until it sees one with which it can recommence parsing.

#### EXAMPLE 2.49

Exceptions in a recursive descent parser

As noted in Section 2.3.1, the ANTLR parser generator takes a CFG as input and builds a human-readable recursive descent parser. Compiler writers have the option of generating Java, C#, or C++, all of which have exception-handling mechanisms. When an ANTLR-generated parser encounters a syntax error, it throws a MismatchedTokenException or NoViableAltException. By default ANTLR includes a handler for these exceptions in every nonterminal subroutine. The handler prints an error message, deletes tokens until it finds something in the FOLLOW set of the nonterminal, and then returns. The compiler writer can define alternative handlers if desired on a production-by-production basis.

#### **Error Productions**

As a general rule, it is desirable for an error recovery technique to be as languageindependent as possible. Even in a recursive descent parser, which is handwritten for a particular language, it is nice to be able to encapsulate error recovery in the check\_for\_error and match subroutines. Sometimes, however, one can obtain much better repairs by being highly language specific.

Most languages have a few unintuitive rules that programmers tend to violate in predictable ways. In Pascal, for example, semicolons are used to separate statements, but many programmers think of them as *terminating* statements instead. Most of the time the difference is unimportant, since a statement is allowed to be empty. In the following, for example,

```

begin

x := (-b + sqrt(b*b -4*a*c)) / (2*a);

writeln(x);

end;

```

the compiler parses the begin... end block as a sequence of three statements, the third of which is empty. In the following, however,

the compiler must complain, since the then part of an if...then...else construct must consist of a single statement in Pascal. A Pascal semicolon is never allowed immediately before an else, but programmers put them there all the time. Rather than try to tune a general recovery or repair algorithm to deal correctly with this problem, most Pascal compiler writers modify the grammar: they include an extra production that allows the semicolon, but causes the semantic analyzer to print a warning message, telling the user that the semicolon shouldn't be there. Similar error productions are used in C compilers to cope with "anachronisms" that have crept into the language as it evolved. Syntax that was valid only in early versions of C is still accepted by the parser, but evokes a warning message.

#### EXAMPLE 2.50

Error production for "; else"

#### Error Recovery in Table-Driven LL Parsers

Given the similarity to recursive descent parsing, it is straightforward to implement phrase-level recovery in a table-driven top-down parser. Whenever we encounter an error entry in the parse table, we simply delete input tokens until we find a member of a statically defined set of starter symbols (including \$\$), or a member of the FIRST or FOLLOW set of the nonterminal at the top of the parse stack.<sup>1</sup> If we find a member of the FIRST set, we continue the main loop of the driver. If we find a member of the FOLLOW set or the starter set, we pop the nonterminal off the parse stack first. If we encounter an error in match, rather than in the parse table, we simply pop the token off the parse stack.

But we can do better than this! Since we have the entire parse stack easily accessible (it was hidden in the control flow and procedure calling sequence of recursive descent), we can enumerate all possible combinations of insertions and deletions that would allow us to continue parsing. Given appropriate metrics, we can then evaluate the alternatives to pick the one that is in some sense "best."

Because perfect error recovery (actually error *repair*) would require that we read the programmer's mind, any practical technique to evaluate alternative "corrections" must rely on heuristics. For the sake of simplicity, most compilers limit themselves to heuristics that (1) require no semantic information, (2) do not require that we "back up" the parser or the input stream (i.e., to some state prior to the one in which the error was detected), and (3) do not change the spelling of tokens or the boundaries between them. A particularly elegant algorithm that conforms to these limits was published by Fischer, Milton, and Quiring in 1980 [FMQ80, FL88]. As originally described, the algorithm was limited to languages in which programs could always be corrected by inserting appropriate tokens into the input stream, without ever requiring deletions. It is relatively easy, however, to extend the algorithm first; the version with deletions employs it as a subroutine. We do not consider substitutions here.<sup>2</sup>

The FMQ error-repair algorithm requires the compiler writer to assign an insertion cost C(t) and a deletion cost D(t) to every token t. (Since we cannot change where the input ends, we have  $C(\$\$)=D(\$\$)=\infty$ .) In any given error situation, the algorithm chooses the least cost combination of insertions and

I This description uses global FOLLOW sets. If we want to use context-specific look-aheads instead, we can peek farther down in the stack. A token is an acceptable context-specific look-ahead if it is in the FIRST set of the second symbol *A* from the top in the stack or, if it would cause us to predict  $A \longrightarrow \epsilon$ , the FIRST set of the third symbol *B* from the top or, if it would cause us to predict  $B \longrightarrow \epsilon$ , the FIRST set of the fourth symbol from the top, and so on.

**<sup>2</sup>** A substitution can always be effected as a deletion/insertion pair, but we might want ideally to give it special consideration. For example, we probably want to be cautious about deleting a left square bracket or inserting a left parenthesis, since both of these symbols must be matched by something later in the input, at which point we are likely to see cascading errors. But substituting a left parenthesis for a left square bracket is in some sense more plausible, especially given the differences in array subscript syntax in different programming languages.

deletions that allows the parser to consume one more token of real input. The state of the parser is never changed; only the input is modified (rather than pop a stack symbol, the repair algorithm pushes its yield onto the input stream).

As in phrase-level recovery in a recursive descent parser, the FMQ algorithm needs to address the immediate error detection problem. There are several ways we could do this. One would be to use a "full LL" parser, which keeps track of local FOLLOW sets. Another would be to inspect the stack when predicting an epsilon production, to see if what lies underneath will allow us to accept the incoming token. The first option significantly increases the size and complexity of the parser. The second option leads to a nonlinear-time parsing algorithm. Fortunately, there is a third option. We can save all changes to the stack (and calls to the semantic analyzer's action routines) in a temporary buffer until the match routine accepts another real token of input. If we discover an error before we accept a real token, we undo the stack changes and throw away the buffered calls to action routines. Then we can pretend we recognized the error when a full LL parser would have.

We now consider the task of repairing with only insertions. We begin by extending the notion of insertion costs to strings in the obvious way: if  $w = a_1 a_2 \dots a_n$ , we have  $C(w) = \sum_{i=1}^{n} C(a_i)$ . Using the cost function *C*, we then build a pair of tables *S* and *E*. The *S* table is one-dimensional, and is indexed by grammar symbol. For any symbol *X*, S(X) is a least-cost string of terminals derivable from *X*. That is,

$$S(X) = w \iff X \Longrightarrow^* w \text{ and } \forall x \text{ such that } X \Longrightarrow^* x, \ C(w) \le C(x)$$

Clearly  $S(a) = a \forall$  tokens a.

The *E* table is two-dimensional, and is indexed by symbol/token pairs. For any symbol *X* and token a,  $E(X, \mathbf{a})$  is the lowest-cost prefix of a in *X*; that is, the lowest cost token string *w* such that  $X \Longrightarrow^* wax$ . If *X* cannot yield a string containing a, then  $E(X, \mathbf{a})$  is defined to be a special symbol ?? whose insertion cost is  $\infty$ . If  $X = \mathbf{a}$ , or if  $X \Longrightarrow^* \mathbf{a}x$ , then  $E(X, \mathbf{a}) = \epsilon$ , where  $C(\epsilon) = 0$ .

To find a least-cost insertion that will repair a given error, we execute the function find\_insertion, shown in Figure (2.30). The function begins by considering the least-cost insertion that will allow it to derive the input token from the symbol at the top of the stack (there may be none). It then considers the possibility of "deleting" that top-of-stack symbol (by inserting its least-cost yield into the input stream) and deriving the input token from the second symbol on the stack. It continues in this fashion, considering ways to derive the input token from ever deeper symbols on the stack, until the cost of inserting the yields of the symbols above exceeds the cost of the cheapest repair found so far. If it reaches the bottom of the stack without finding a finite-cost repair, then the error cannot be repaired by insertions alone.

To produce better-quality repairs, and to handle languages that cannot be repaired with insertions only, we need to consider deletions. As we did with the insert cost vector C, we extend the deletion cost vector D to strings of tokens in

example 2.51

Insertion-only repair in FMQ

example 2.52

FMQ with deletions

```

function find_insertion(\mathbf{a} : token) : string

-- assume that the parse stack consists of symbols X_n, \ldots X_2, X_1,

-- with X_n at top-of-stack

ins := ??

prefix := \epsilon

for i in n \ldots 1

if C(\text{prefix}) \ge C(\text{ins})

-- no better insertion is possible

return ins

if C(\text{prefix} . E(X_i, \mathbf{a})) < C(\text{ins})

-- better insertion found

ins := prefix . E(X_i, \mathbf{a})

prefix := prefix . S(X_i)

return ins

```

Figure 2.30 Outline of a function to find a least-cost insertion that will allow the parser to accept the input token *a*. The dot character (.) is used here for string concatenation.

```

function find_repair : string, int

```

```

-- assume that the parse stack consists of symbols X_n, \ldots X_2, X_1,

-- with X_n at top-of-stack,

-- and that the input stream consists of tokens a_1, a_2, a_3, \ldots

i := 0

-- number of tokens we're considering deleting

best_ins := ??

best_del := 0

loop

cur_ins := find_insertion(\mathbf{a}_{i+1})

if C(\text{cur}_i\text{ins}) + D(\mathbf{a}_1 \dots \mathbf{a}_i) < C(\text{best}_i\text{ins}) + D(\mathbf{a}_1 \dots \mathbf{a}_{\text{best}_i\text{del}})

-- better repair found

best_ins := cur_ins

best_del := i

i + := 1

if D(\mathbf{a}_1 \dots \mathbf{a}_i) > C(\text{best_ins}) + D(\mathbf{a}_1 \dots \mathbf{a}_{\text{best_del}})

-- no better repair is possible

return (best_ins, best_del)

```

Figure 2.31 Outline of a function to find a least-cost combination of insertions and deletions that will allow the parser to accept one more token of input.

the obvious way. We then embed calls to find\_insertion in a second loop, shown in Figure (2.31. This loop repeatedly considers deleting more and more tokens, each time calling find\_insertion on the remaining input, until the cost of deleting additional tokens exceeds the cost of the cheapest repair found so far. The search can never fail; it is always possible to find a combination of insertions and deletions that will allow the end-of-file token to be accepted. Since the algorithm may need to consider (and then reject) the option of deleting an arbitrary number of tokens, the scanner must be prepared to peek an arbitrary distance ahead in the input stream and then back up again.

The FMQ algorithm has several desirable properties. It is simple and efficient (given that the grammar is bounded in size, we can prove that the time to choose a repair is bounded by a constant). It can repair an arbitrary input string. Its decisions are locally optimal, in the sense that no cheaper repair can allow the parser to make forward progress. It is table-driven and therefore fully automatic. Finally, it can be tuned to prefer "likely" repairs by modifying the insertion and deletion costs of tokens. Some obvious heuristics include:

- Deletion should usually be more expensive than insertion.

- Common operators (e.g., multiplication) should have lower cost than uncommon operators (e.g., modulo division) in the same place in the grammar.

- Starter symbols (e.g., begin, if, () should have higher cost than their corresponding final symbols (end, fi, )).

- "Noise" symbols (comma, semicolon, do) should have very low cost.

### Error Recovery in Bottom-Up Parsers

Locally least-cost repair is possible in bottom-up parsers, but it isn't as easy as it is in top-down parsers. The advantage of a top-down parser is that the content of the parse stack unambiguously identifies the context of an error, and specifies the constructs expected in the future. The stack of a bottom-up parser, by contrast, describes a set of possible contexts, and says nothing explicit about the future.

In practice, most bottom-up parsers tend to rely on panic-mode or phrase-level recovery. The intuition is that when an error occurs, the top few states on the parse stack represent the shifted prefix of an erroneous construct. Recovery consists of popping these states off the stack, deleting the remainder of the construct from the incoming token stream, and then restarting the parser, possibly after shifting a fictitious nonterminal to represent the erroneous construct.

Unix's yacc/bison provides a typical example of bottom-up phrase-level recovery. In addition to the usual tokens of the language, yacc/bison allows the compiler writer to include a special token, error, anywhere in the right-hand sides of grammar productions. When the parser built from the grammar detects a syntax error, it

- I. Calls the function yyerror, which the compiler writer must provide. Normally, yyerror simply prints a message (e.g., "parse error"), which yacc/bison passes as an argument

- **2.** Pops states off the parse stack until it finds a state in which it can shift the error token (if there is no such state, the parser terminates)

- 3. Inserts and then shifts the error token

- **4.** Deletes tokens from the input stream until it finds a valid look-ahead for the new (post error) context

- 5. Temporarily disables reporting of further errors

- 6. Resumes parsing

If there are any semantic action routines associated with the production containing the error token, these are executed in the normal fashion. They can do such things as print additional error messages, modify the symbol table, patch up semantic processing, prompt the user for additional input in an interactive tool (yacc/bison can be used to build things other than batch-mode compilers), or disable code generation. The rationale for disabling further syntax errors is to make sure that we have really found an acceptable context in which to resume parsing before risking cascading errors. Yacc/bison automatically re-enables the reporting of errors after successfully shifting three real tokens of input. A semantic action routine can re-enable error messages sooner if desired by calling the built-in routine yyerrorok.

For our example calculator language, we can imagine building a yacc/bison parser using the bottom-up grammar of Figure 2.24. For panic-mode recovery, we might want to back out to the nearest statement:

```

stmt \longrightarrow error {printf("parsing resumed at end of current statement\n");}

```

The semantic routine written in curly braces would be executed when the parser recognizes  $stmt \longrightarrow error$ .<sup>3</sup> Parsing would resume at the next token that can follow a statement—in our calculator language, at the next id, read, write, or \$\$.

A weakness of the calculator language, from the point of view of error recovery, is that the current, erroneous statement may well contain additional ids. If we resume parsing at one of these, we are likely to see another error right away. We could avoid the error by disabling error messages until several real tokens have been shifted. In a language in which every statement ends with a semicolon, we could have more safely written:

```

stmt \longrightarrow error;

{printf("parsing resumed at end of current statement\n");}

```

In both of these examples we have placed the error symbol at the beginning of a right-hand side, but there is no rule that says it must be so. We might decide, for example, that we will abandon the current statement whenever we see an error, unless the error happens inside a parenthesized expression, in which case we will attempt to resume parsing after the closing parenthesis. We could then add the following production:

```

factor --> ( error )

{printf("parsing resumed at end of

parenthesized expression\n");}

```

#### EXAMPLE 2.53

Panic mode in yacc/bison

### example 2.54

Panic mode with statement terminators

```

EXAMPLE 2.55

```

Phrase-level recovery in yacc/bison

<sup>3</sup> The syntax shown here is not the same as that accepted by yacc/bison, but is used for the sake of consistency with earlier material.

In the CFSM of Figure 2.25, it would then be possible in State 8 to shift error, delete some tokens, shift ), recognize *factor*, and continue parsing the surrounding expression. Of course, if the erroneous expression contains nested parentheses, the parser may not skip all of it, and a cascading error may still occur.

Because yacc/bison creates LALR parsers, it automatically employs contextspecific look-ahead, and does not usually suffer from the immediate error detection problem. (A full LR parser would do slightly better.) In an SLR parser, a good error recovery algorithm needs to employ the same trick we used in the top-down case. Specifically, we buffer all stack changes and calls to semantic action routines until the shift routine accepts a real token of input. If we discover an error before we accept a real token, we undo the stack changes and throw away the buffered calls to semantic routines. Then we can pretend we recognized the error when a full LR parser would have.

### CHECK YOUR UNDERSTANDING

- 45. Why is syntax error recovery important?

- **46**. What are *cascading errors*?

- 47. What is panic mode? What is its principal weakness?

- 48. What is the advantage of *phrase-level recovery* over panic mode?

- 49. What is the *immediate error detection problem*, and how can it be addressed?

- 50. Describe two situations in which context-specific FOLLOW sets may be useful.

- **51**. Outline Wirth's mechanism for error recovery in recursive descent parsers. Compare this mechanism to exception-based recovery.

- **52.** What are *error productions*? Why might a parser that incorporates a high-quality, general-purpose error recovery algorithm still benefit from using such productions?

- 53. Outline the FMQ algorithm. In what sense is the algorithm optimal?

- 54. Why is error recovery more difficult in bottom-up parsers than it is in top-down parsers?

- 55. Describe the error recovery mechanism employed by yacc/bison.

# Programming Language Syntax

# 2.4 Theoretical Foundations

As noted in the main text, scanners and parsers are based on the finite automata and pushdown automata that form the bottom two levels of the Chomsky language hierarchy. At each level of the hierarchy, machines can be either *deterministic* or *nondeterministic*. A deterministic automaton always performs the same operation in a given situation. A nondeterministic automaton can perform any of a *set* of operations. A nondeterministic machine is said to accept a string if there exists a choice of operation in each situation that will eventually lead to the machine saying "yes." As it turns out, nondeterministic and deterministic finite automata are equally powerful: every DFA is, by definition, a degenerate NFA, and the construction in Example 2.14 (page 56) demonstrates that for any NFA we can create a DFA that accepts the same language. The same is not true of push-down automata: there are context-free languages that are accepted by an NPDA but not by any DPDA. Fortunately, DPDAs suffice in practice to accept the syntax of real programming languages. Practical scanners and parsers are always deterministic.

### 2.4. Finite Automata

Precisely defined, a deterministic finite automaton (DFA) M consists of (1) a finite set Q of *states*, (2) a finite alphabet  $\Sigma$  of input symbols, (3) a distinguished *initial* state  $q_1 \in Q$ , (4) a set of distinguished *final* states  $F \subseteq Q$ , and (5) a *transition function*  $\delta : Q \times \Sigma \rightarrow Q$  that chooses a new state for M based on the current state and the current input symbol. M begins in state  $q_1$ . One by one it consumes its input symbols, using  $\delta$  to move from state to state. When the final symbol has been consumed, M is interpreted as saying "yes" if it is in a state in F; otherwise it is interpreted as saying "no." We can extend  $\delta$  in the obvious way to take strings, rather than symbols, as inputs, allowing us to say that M accepts string x if  $\delta(q_1, x) \in F$ . We can then define L(M), the language accepted by M, to be the set  $\{x \mid \delta(q_1, x) \in F\}$ . In a nondeterministic finite automaton (NFA),

Figure 2.32 Minimal DFA for the language consisting of all strings of decimal digits containing a single decimal point. Adapted from Figure 2.10 in the main text. The symbol d here is short for "0, 1, 2, 3, 4, 5, 6, 7, 8, 9".

the transition function,  $\delta$ , is multivalued: the automaton can move to any of a *set* of possible states from a given state on a given input. In addition, it may move from one state to another "spontaneously"; such transitions are said to take input symbol  $\epsilon$ .

We can illustrate these definitions with an example. Consider the circles-andarrows automaton of Figure (2.32 (adapted from Figure 2.10 in the main text). This is the minimal DFA accepting strings of decimal digits containing a single decimal point.  $\Sigma = \{0, 1, 2, 3, 4, 5, 6, 7, 8, 9, .\}$  is the machine's input alphabet.  $Q = \{q_1, q_2, q_3, q_4\}$  is the set of states;  $q_1$  is the initial state;  $F = \{q_4\}$  (a singleton in this case) is the set of final states. The transition function can be represented by a set of triples  $\delta = \{(q_1, 0, q_2), \dots, (q_1, 9, q_2), (q_1, ., q_3), (q_2, 0, q_2), \dots, (q_2, 9, q_2), (q_2, ., q_4), (q_3, 0, q_4), \dots, (q_3, 9, q_4), (q_4, 0, q_4), \dots, (q_4, 9, q_4)\}$ . In each triple  $(q_i, a, q_j), \delta(q_i, a) = q_j$ .

Given the constructions of Examples 2.12 and 2.14, we know that there exists an NFA that accepts the language generated by any given regular expression, and a DFA equivalent to any given NFA. To show that regular expressions and finite automata are of equivalent expressive power, all that remains is to demonstrate that there exists a regular expression that generates the language accepted by any given DFA. We illustrate the required construction below for our decimal strings example (Figure ©2.32). More formal and general treatment of all the regular language constructions can be found in standard automata theory texts [HMU01, Sip97].

#### From a DFA to a Regular Expression

To construct a regular expression equivalent to a given DFA, we employ a a dynamic programming algorithm that builds solutions to successively more complicated subproblems from a table of solutions to simpler subproblems. We begin with a set of simple regular expressions that describe the transition function,  $\delta$ . For all states *i*, we define

$$r_{ii}^0 = \mathbf{a}_1 \mid \mathbf{a}_2 \mid \ldots \mid \mathbf{a}_m \mid \epsilon$$

EXAMPLE 2.56

Formal DFA for  $d^*(.d | d.) d^*$

where  $\{a_1 \mid a_2 \mid \ldots \mid a_m\} = \{a \mid \delta(q_i, a) = q_i\}$  is the set of characters labeling the "self-loop" from state  $q_i$  back to itself. If there is no such self-loop,  $r_{ij}^0 = \epsilon$ . Similarly, for  $i \neq j$ , we define

$$r_{ij}^0 = \mathbf{a}_1 \mid \mathbf{a}_2 \mid \ldots \mid \mathbf{a}_m$$

where  $\{a_1 \mid a_2 \mid \dots \mid a_m\} = \{a \mid \delta(q_i, a) = q_j\}$  is the set of characters labeling the arc from  $q_i$  to  $q_j$ . If there is no such arc,  $r_{ij}^0$  is the empty regular expression. (Note the difference here: we can stay in state  $q_i$  by not accepting any input, so  $\epsilon$ is always one of the alternatives in  $r_{ij}^0$ , but not in  $r_{ij}^0$  when  $i \neq j$ .)

Given these  $r^0$  expressions, the dynamic programming algorithm inductively calculates expressions  $r_{ij}^k$  with larger superscripts. In each, k names the highest-numbered state through which control may pass on the way from  $q_i$  to  $q_j$ . We assume that states are numbered starting with  $q_1$ , so when k = 0 we must transition directly from  $q_i$  to  $q_j$ , with no intervening states.

In our small example DFA,  $r_{11}^0 = r_{33}^0 = \epsilon$ , and  $r_{22}^0 = r_{44}^0 = 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | <math>\epsilon$ , which we will abbreviate  $d | \epsilon$ . Similarly,  $r_{13}^0 = r_{24}^0 = .$ , and  $r_{12}^0 = r_{34}^0 = d$ . Expressions  $r_{14}^0$ ,  $r_{21}^0$ ,  $r_{23}^0$ ,  $r_{31}^0$ ,  $r_{32}^0$ ,  $r_{41}^0$ ,  $r_{42}^0$ , and  $r_{43}^0$  are all empty.

For k > 0, the  $r_{ij}^k$  expressions will generally generate multicharacter strings. At each step of the dynamic programming algorithm, we let

$$r_{ij}^{k} = r_{ij}^{k-1} \mid r_{ik}^{k-1} r_{kk}^{k-1} \star r_{kj}^{k-1}$$

That is, to get from  $q_i$  to  $q_j$  without going through any states numbered higher than k, we can either go from  $q_i$  to  $q_j$  without going through any state numbered higher than k - 1 (which we already know how to do), or else we can go from  $q_i$  to  $q_k$  (without going through any state numbered higher than k - 1), travel out from  $q_k$  and back again an arbitrary number of times (never visiting a state numbered higher than k - 1 in between), and finally go from  $q_k$  to  $q_j$  (again without visiting a state numbered higher than k - 1). If any of the constituent regular expressions is empty, we omit its term of the outermost alternation. At the end, our overall answer is  $r_{1f_1}^n | r_{1f_2}^n | \dots | r_{1f_t}^n$ , where n = |Q| is the total number of states and  $F = \{q_{f_1}, q_{f_2}, \dots, q_{f_t}\}$  is the set of final states.

Because  $r_{11}^0 = \epsilon$  and there are no transitions from States 2, 3, or 4 to State 1, nothing changes in the first inductive step in our example; that is,  $\forall i [r_{ii}^1 = r_{ii}^0]$ . The second step is a bit more interesting. Since we are now allowed to go through State 2, we have  $r_{22}^2 = r_{22}^2 r_{22}^2 * r_{22}^2 = (d | \epsilon) | (d | \epsilon) | (d | \epsilon)^* | (d | \epsilon) | = d^*$ . Because  $r_{21}^1, r_{23}^1, r_{32}^1$ , and  $r_{42}^1$  are empty, however,  $r_{11}^2, r_{33}^2$ , and  $r_{44}^2$  remain the same as  $r_{11}^1, r_{13}^1, and r_{44}^1$ . In a similar vein, we have

$$r_{12}^{2} = d \mid d (d \mid \epsilon)^{*} (d \mid \epsilon) = d^{+}$$

$$r_{14}^{2} = d (d \mid \epsilon)^{*} = d^{+} .$$

$$r_{24}^{2} = . \mid (d \mid \epsilon) (d \mid \epsilon)^{*} = d^{*} .$$

#### EXAMPLE 2.57

Reconstructing a regular expression for the decimal string DFA Missing transitions and empty expressions from the previous step leave  $r_{13}^2 = r_{13}^1 = .$  and  $r_{34}^2 = r_{34}^1 = d$ . Expressions  $r_{21}^2$ ,  $r_{23}^2$ ,  $r_{31}^2$ ,  $r_{32}^2$ ,  $r_{41}^2$ ,  $r_{42}^2$ , and  $r_{43}^2$  remain empty.

In the third inductive step, we have

$$r_{13}^{3} = . \mid . \epsilon^{*} \epsilon = .$$

$$r_{14}^{3} = d^{+} . \mid . \epsilon^{*} d = d^{+} . \mid . d$$

$$r_{34}^{3} = d \mid \epsilon \epsilon^{*} d = d$$

All other expressions remain unchanged from the previous step.

Finally, we have

$$r_{14}^{4} = (d^{+} \cdot | \cdot d) | (d^{+} \cdot | \cdot d) (d | \epsilon)^{*} (d | \epsilon)$$

$$= (d^{+} \cdot | \cdot d) | (d^{+} \cdot | \cdot d) d^{*}$$

$$= (d^{+} \cdot | \cdot d) d^{*}$$

$$= d^{+} \cdot d^{*} | \cdot d^{+}$$

Since *F* has a single member  $(q_4)$ , this expression is our final answer.

#### Space Requirements

In Section 2.2.1 we noted without proof that the conversion from an NFA to a DFA may lead to exponential blow-up in the number of states. Certainly this did not happen in our decimal string example: the NFA of Figure 2.8 has 14 states, while the equivalent DFA of Figure 2.9 has only 7, and the minimal DFA of Figures 2.10 and @2.32 has only 4.

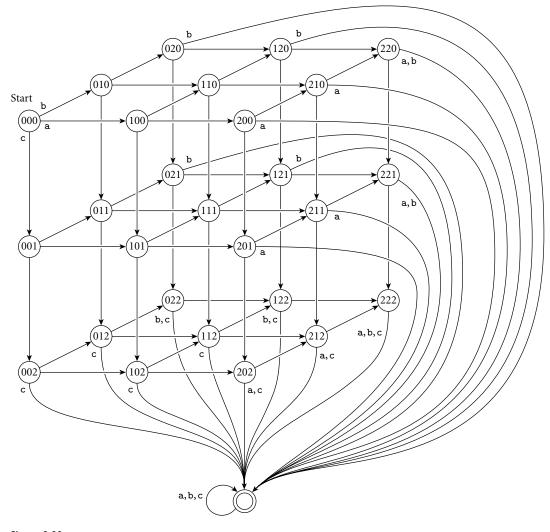

Consider, however, the subset of  $(a | b | c)^*$  in which some letter appears at least three times. The minimal DFA for this language has 28 states. As shown in Figure (2.33, 27 of these are states in which we have seen *i*, *j*, and *k* as, bs, and cs, respectively. The 28th (and only final) state is reached once we have seen at least three of some specific character.

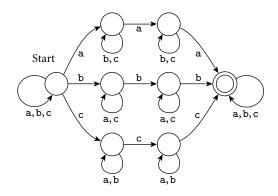

By contrast, there exists an NFA for this language with only eight states, as shown in Figure (o2.34. It requires that we "guess," at the outset, whether we will see three as, three bs, or three cs. It mirrors the structure of the natural regular expression (a | b | c)\* a (a | b | c)\* a (a | b | c)\* | (a | b | c)\* b (a | b | c)\* b (a | b | c)\* | (a | b | c)\* c (a | b | c)\* c (a | b | c)\*.

Of course, the eight-state NFA does not emerge directly from the construction of Section 2.2.1; that construction produces a 52-state machine with a certain amount of redundancy, and with many extraneous states and epsilon productions. But consider the similar subset of  $(0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9)^*$  in which some digit appears at least ten times. The minimal DFA for this language has 10,000,000,001 states: a non-final state for each combination of zeros through nines with less than ten of each, and a single final state reached once any digit has appeared at least ten times. One possible regular expression for this language is

EXAMPLE 2.58

A regular language with a large minimal DFA

#### EXAMPLE 2.59

Exponential DFA blow-up

Figure 2.33 DFA for the language consisting of all strings in  $(a | b | c)^*$  in which some letter appears at least three times. State name *ijk* indicates that *i* as, *j* bs, and *k* cs have been seen so far. Within the cubic portion of the figure, most edge labels are elided: a transitions move to the right, **b** transitions go back into the page, and **c** transitions move down.

Copyright © 2009 by Elsevier Inc. All rights reserved.

Figure 2.34 NFA corresponding to the DFA of Figure @2.33.

Our construction would yield a very large NFA for this expression, but clearly many orders of magnitude smaller than ten billion states!

### 2.4.2 Push-Down Automata

A deterministic push-down automaton (DPDA) N consists of (1) Q, (2)  $\Sigma$ , (3)  $q_1$ , and (4) F, as in a DFA, plus (6) a finite alphabet  $\Gamma$  of stack symbols, (7) a distinguished initial stack symbol  $Z_1 \in \Gamma$ , and (5') a transition function  $\delta$  :  $Q \times \Gamma \times {\Sigma \cup {\epsilon}} \rightarrow Q \times \Gamma^*$ , where  $\Gamma^*$  is the set of strings of zero or more symbols from  $\Gamma$ . N begins in state  $q_1$ , with symbol  $Z_1$  in an otherwise empty stack. It repeatedly examines the current state q and top-of-stack symbol Z. If  $\delta(q,\epsilon,Z)$  is defined, N moves to state r and replaces Z with  $\alpha$  in the stack, where  $(r, \alpha) = \delta(q,\epsilon,Z)$ . In this case N does not consume its input symbol. If  $\delta(q,\epsilon,Z)$ is undefined, N examines and consumes the current input symbol a. It then moves to state s and replaces Z with  $\beta$ , where  $(s, \beta) = \delta(q, a, Z)$ . N is interpreted as accepting a string of input symbols if and only if it consumes the symbols and ends in a state in F.

As with finite automata, a nondeterministic push-down automaton (NPDA) is distinguished by a multivalued transition function: an NPDA can choose any of a set of new states and stack symbol replacements when faced with a given state, input, and top-of-stack symbol. If  $\delta(q, \epsilon, Z)$  is nonempty, N can also choose a new state and stack symbol replacement without inspecting or consuming its current input symbol. While we have seen that nondeterministic and deterministic finite automata are equally powerful, this correspondence does not carry over to pushdown automata: there are context-free languages that are accepted by an NPDA but not by any DPDA.

The proof that CFGs and NPDAs are equivalent in expressive power is more complex than the corresponding proof for regular expressions and finite automata. The proof is also of limited practical importance for compiler construction; we do not present it here. While it is possible to create an NPDA for any CFL, that NPDA may in some cases require exponential time to recognize strings in the language. (The  $O(n^3)$  algorithms mentioned in Section 2.3 do not take the form of PDAs.) Practical programming languages can all be expressed with LL or LR grammars, which can be parsed with a (deterministic) PDA in linear time.

An LL(1) PDA is very simple. Because it makes decisions solely on the basis of the current input token and top-of-stack symbol, its state diagram is trivial. All but one of the transitions is a self-loop from the initial state to itself. A final transition moves from the initial state to a second, final state when it sees \$\$ on the input and the stack. As we noted in Section 2.3.3 (page 91), the state diagram for an SLR(1) or LALR(1) parser is substantially more interesting: it's the characteristic finite-state machine (CFSM). Full LR(1) parsers have similar machines, but usually with many more states, due to the need for path-specific look-ahead.

A little study reveals that if we define every state to be accepting, then the CFSM, without its stack, is a DFA that recognizes the grammar's *viable prefixes*. These are all the strings of grammar symbols that can begin a sentential form in the canonical (right-most) derivation of some string in the language, and that do not extend beyond the end of the handle. The algorithms to construct LL(1) and SLR(1) PDAs from suitable grammars were given in Sections 2.3.2 and 2.3.3.

### 2.4.3 Grammar and Language Classes

As we noted in Section 2.1.2, a scanner is incapable of recognizing arbitrarily nested constructs. The key to the proof is to realize that we cannot count an arbitrary number of left-bracketing symbols with a finite number of states. Consider, for example, the problem of accepting the language  $0^n 1^n$ . Suppose there is a DFA M that accepts this language. Suppose further that M has m states. Now suppose we feed M a string of m + 1 zeros. By the *pigeonhole principle* (you can't distribute m objects among p < m pigeonholes without putting at least two objects in some pigeonhole), M must enter some state  $q_i$  twice while scanning this string. Without loss of generality, let us assume it does so after seeing j zeros and again after seeing k zeros, for  $j \neq k$ . Since we know that M accepts the string  $0^j 1^j$  and the string  $0^k 1^k$ , and since it is in precisely the same state after reading  $0^j$  and  $0^k$ , we can deduce that M must also accept the strings  $0^j 1^k$  and  $0^k 1^j$ . Since these strings are not in the language, we have a contradiction: M cannot exist.

Within the family of context-free languages, one can prove similar theorems about the constructs that can and cannot be recognized using various parsing algorithms. Though almost all real parsers get by with a single token of lookahead, it is possible in principle to use more than one, thereby expanding the set of grammars that can be parsed in linear time. In the top-down case we can redefine FIRST and FOLLOWsets to contain pairs of tokens in a more or less straightforward fashion. If we do this, however, we encounter a more serious

#### EXAMPLE 2.60

0<sup>n</sup>1<sup>n</sup> is not a regular language version of the immediate error detection problem described in Section O2.3.4. There we saw that the use of context-independent FOLLOW sets could cause us to overlook a syntax error until after we had needlessly predicted one or more epsilon productions. Context-specific FOLLOW sets solved the problem, but did not change the set of *valid* programs that could be parsed with one token of look-ahead. If we define LL(k) to be the set of all grammars that can be parsed predictively using the top-of-stack symbol and k tokens of look-ahead, then it turns out that for k > 1 we must adopt a context-specific notion of FOLLOW sets in order to parse correctly. The algorithm of Section 2.3.2, which is based on context-independent FOLLOW sets, is actually known as SLL (simple LL), rather than true LL. For k = 1, the LL(1) and SLL(1) algorithms can parse the same set of grammars. For k > 1, LL is strictly more powerful. Among the bottom-up parsers, the relationships among SLR(k), LALR(k), and LR(k) are somewhat more complicated, but extra look-ahead always helps.

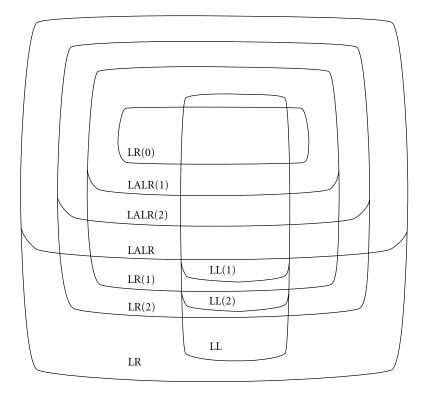

Containment relationships among the classes of grammars accepted by popular linear-time algorithms appear in Figure (© 2.35. The LR class (no suffix) contains every grammar *G* for which there exists a *k* such that  $G \in LR(k)$ ; LL, SLL, SLR, and LALR are similarly defined. Grammars can be found in every region of the figure. Examples appear in Figure (© 2.36. Proofs that they lie in the regions claimed are deferred to Exercise (© 2.30.

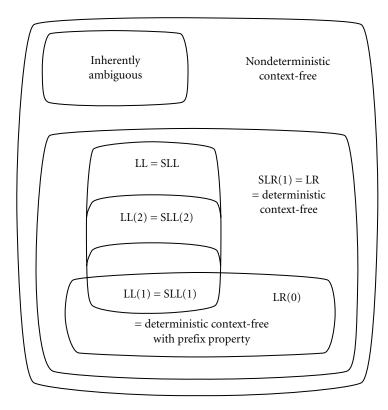

For any context-free grammar *G* and parsing algorithm *P*, we say that *G* is a *P* grammar (e.g., an LL(1) grammar) if it can be parsed using that algorithm. By extension, for any context-free *language L*, we say that *L* is a *P* language if there exists a *P* grammar for *L* (this may not be the grammar we were given). Containment relationships among the classes of languages accepted by the popular parsing algorithms appear in Figure (© 2.37. Again, languages can be found in every region. Examples appear in Figure (© 2.38; proofs are deferred to Exercise (© 2.31.

Note that every context-free language that can be parsed deterministically has an SLR(1) grammar. Moreover, any language that can be parsed deterministically and in which no valid string can be extended to create another valid string (this is called the *prefix property*) has an LR(0) grammar. If we restrict our attention to languages with an explicit \$\$ marker at end-of-file, then they all have the prefix property, and therefore LR(0) grammars.

The relationships among language classes are not as rich as the relationships among grammar classes. Most real programming languages can be parsed by any of the popular parsing algorithms, though the grammars are not always pretty, and special-purpose "hacks" may sometimes be required when a language is almost, but not quite, in a given class. The principal advantage of the more powerful parsing algorithms (e.g., full LR) is that they can parse a wider variety of grammars for a given language. In practice this flexibility makes it easier for the compiler writer to find a grammar that is intuitive and readable, and that facilitates the creation of semantic action routines.

example 2.61

Separation of grammar classes

#### EXAMPLE 2.62

Separation of language classes

**Figure 2.35** Containment relationships among popular grammar classes. In addition to the containments shown, SLL(k) is just inside LL(k), for  $k \ge 2$ , but has the same relationship to everything else, and SLR(k) is just inside LALR(k), for  $k \ge 1$ , but has the same relationship to everything else.

LL(2) but not SLL: SLL(k) and SLR(k) but not LR(k - 1):  $S \longrightarrow A \mathbf{a}^{k-1} \mathbf{b} \mid B \mathbf{a}^{k-1} \mathbf{c}$  $S \longrightarrow a A a | b A b a$  $A \longrightarrow \mathbf{b} \mid \epsilon$  $A \longrightarrow \epsilon$  $B \longrightarrow \epsilon$ SLL(k) but not LL(k - 1):  $S \longrightarrow \mathbf{a}^{k-1} \mathbf{b} \mid \mathbf{a}^k$ LALR(1) but not SLR:  $S \longrightarrow b A b | A c | a b$ LR(0) but not LL:  $A \longrightarrow \mathbf{a}$  $S \longrightarrow A b$ LR(1) but not LALR:  $A \longrightarrow A \mathbf{a} \mid \mathbf{a}$  $S \longrightarrow a \ C \ a \ | \ b \ C \ b \ | \ a \ D \ b \ |$ SLL(1) but not LALR: b D a  $S \longrightarrow A \texttt{a} \mid B \texttt{b} \mid \texttt{c} C$  $C \longrightarrow c$  $C \longrightarrow A \mathbf{b} \mid B \mathbf{a}$  $D \longrightarrow \mathbf{c}$  $A \longrightarrow D$ Unambiguous but not LR:  $B \longrightarrow D$  $D \longrightarrow \epsilon$  $S \longrightarrow a S a | \epsilon$

Figure 2.36 Examples of grammars in various regions of Figure @2.35.

Nondeterministic language:  $\{a^{n}b^{n}c : n \ge 1\} \cup \{a^{n}b^{2n}d : n \ge 1\}$ Inherently ambiguous language:  $\{a^{i}b^{j}c^{k} : i = j \text{ or } j = k ; i, j, k \ge 1\}$ Language with LL(k) grammar but no LL(k-1) grammar:  $\{a^{n}(b \mid c \mid b^{k}d)^{n} : n \ge 1\}$ Language with LR(0) grammar but no LL grammar:  $\{a^{n}b^{n} : n \ge 1\} \cup \{a^{n}c^{n} : n \ge 1\}$

# CHECK YOUR UNDERSTANDING

- 56. What formal machine captures the behavior of a scanner? A parser?

- 57. State three ways in which a real scanner differs from the formal machine.

- 58. What are the formal components of a DFA?

- **59.** Outline the algorithm used to construct a regular expression equivalent to a given DFA.

- **60.** What is the inherent "big-O" complexity of parsing with an NPDA? Why is this worse than the  $O(n^3)$  time mentioned in Section 2.3?

- **6**I. How many states are there in an LL(1) PDA? An SLR(1) PDA? Explain.

- **62**. What are the *viable prefixes* of a CFG?

- **63.** Summarize the proof that a DFA cannot recognize arbitrarily nested constructs.

- **64**. Explain the difference between LL and SLL parsing.

- **65**. Is every LL(1) grammar also LR(1)? Is it LALR(1)?

- 66. Does every LR language have an SLR(1) grammar?

- **67.** Why are the containment relationships among grammar classes more complex than those among language classes?

# Programming Language Syntax

# 2.6 Exercises

- **2.28** Give an example of an erroneous program fragment in which consideration of semantic information (e.g., types) might help one make a good choice between two plausible "corrections" of the input.

- **2.29** Give an example of an erroneous program fragment in which the "best" correction would require one to "back up" the parser (i.e., to undo recent predictions/matches or shifts/reductions).

- **2.30** Prove that the grammars in Figure <sup>(6)</sup>2.36 lie in the regions claimed.

- 2.31 (Difficult) Prove that the languages in Figure ©2.38 lie in the regions claimed.

- **2.32** Prove that regular expressions and *left-linear grammars* are equally powerful. A left-linear grammar is a context-free grammar in which every right-hand side contains at most one nonterminal, and then only at the left-most end.

# Programming Language Syntax

# 2.7 Explorations

- 2.40 Experiment with syntax errors in your favorite compiler. Feed the compiler deliberate errors and comment on the quality of the recovery or repair. How often does it do the "right thing"? How often does it generate cascading errors? Speculate as to what sort of recovery or repair algorithm it might be using.

- 2.41 Spelling mistakes (typos in keywords and identifiers) are a common source of syntax and static semantic errors. Identifying such errors—and guessing what the user meant to type—could result in significantly better error recovery. Discuss how you might go about incorporating spelling correction into some existing error recovery system. (Hint: You might want to consult Morgan's early paper on this subject [Mor70].)

# Names, Scopes, and Bindings

For both static and dynamic scoping, a language implementation must keep track of the name-to-object bindings in effect at each point in the program. The principal difference is *time*: with static scope the compiler uses a *symbol table* to track bindings at compile time; with dynamic scoping the interpreter or run-time system uses an *association list* or *central reference table* to track bindings at run time.

### 3.4. Symbol Tables

In a language with static scoping, the compiler uses an insert operation to place a name-to-object binding into the symbol table for each newly encountered declaration. When it encounters the use of a name that should already have been declared, the compiler uses a lookup operation to search for an existing binding. It is tempting to try to accommodate the visibility rules of static scoping by performing a remove operation to delete a name from the symbol table at the end of its scope. Unfortunately, several factors make this straightforward approach impractical:

- The ability of inner declarations to hide outer ones in most languages with nested scopes means that the symbol table has to be able to contain an arbitrary number of mappings for a given name. The lookup operation must return the innermost mapping, and outer mappings must become visible again at end of scope.

- Records (structures) and classes have some of the properties of scopes, but do not share their nicely nested structure. When it sees a record declaration, the semantic analyzer must remember the names of the record's fields (recursively, if records are nested). At the end of the declaration, the field names must become invisible. Later, however, whenever a variable of the record type appears in the program text (as in my\_rec.field\_name), the record fields

must suddenly become visible again for the part of the reference after the dot. In Pascal and other languages with with statements (Section 7.3.3), field names must become visible in a multi-statement context.

- As noted in Section 3.3.3, names are sometimes used before they are declared. Algol and C, for example, permit *forward references* to labels. Pascal permits forward references in pointer declarations. Modula-3 permits forward references of all kinds.

- As noted in Section 3.3.3, C, C++, and Ada distinguish between the declaration of an object and its definition. Pascal has a similar mechanism for mutually recursive subroutines. When it sees a declaration, the compiler must remember any nonvisible details, so that it can check the eventual definition for consistency. This operation is similar to remembering the field names of records.

- While it may be desirable to forget names at the end of their scope, and even to reclaim the space they occupy in the symbol table, information about them may need to be saved for use by a *symbolic debugger*. The debugger is a tool that allows the user to manipulate a running program: starting it, stopping it, and reading and writing its data. In order to parse high level commands from the user (e.g., to print the value of my\_firm^.revenues [1999]), the debugger must have access to the compiler's symbol table. To make it available at run time, the compiler typically saves the table in a hidden portion of the final machine-language program.

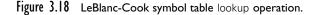

To accommodate these concerns, most compilers never delete anything from the symbol table. Instead, they manage visibility using enter\_scope and leave\_ scope operations. Implementations vary from compiler to compiler; the approach described here is due to LeBlanc and Cook [CL83].

Each scope, as it is encountered, is assigned a serial number. The outermost scope (the one that contains the predefined identifiers), is given number 0. The scope containing programmer-declared global names is given number 1. Additional scopes are given successive numbers as they are encountered. All serial numbers are distinct; they do not represent the level of lexical nesting, except in as much as nested subroutines naturally end up with numbers higher than those of surrounding scopes.

All names, regardless of scope, are entered into a single large hash table, keyed by name. Each entry in the table then contains the symbol name, its category (variable, constant, type, procedure, field name, parameter, etc.), scope number, type (a pointer to another symbol table entry), and additional, category-specific fields.

In addition to the hash table, the symbol table has a *scope stack* that indicates, in order, the scopes that compose the current referencing environment. As the semantic analyzer scans the program, it pushes and pops this stack whenever it enters or leaves a scope, respectively. Entries in the scope stack contain the scope number, an indication of whether the scope is closed, and in some cases further information.

#### EXAMPLE 3.44

The LeBlanc-Cook symbol table

```

procedure lookup(name)

pervasive := best := null

apply hash function to name to find appropriate chain

foreach entry e on chain

if e.name = name

-- not something else with same hash value

if e.scope = 0

pervasive := e

else

foreach scope s on scope stack, top first

if s.scope = e.scope

best := e

– closer instance

exit inner loop

elsif best \neq null and then s.scope = best.scope

exit inner loop

--won't find better

if s.closed

exit inner loop

-- can't see farther

if best \neq null

while best is an import or export entry

best := best.real_entry

return best

elsif pervasive \neq null

return pervasive

else

-- name not found

return null

```

To look up a name in the table, we scan down the appropriate hash chain looking for entries that match the name we are trying to find. For each matching entry, we scan down the scope stack to see if the scope of that entry is visible. We look no deeper in the stack than the top-most closed scope. Imports and exports are made visible outside their normal scope by creating additional entries in the table; these extra entries contain pointers to the real entries. We don't have to examine the scope stack at all for entries with scope number 0: they are pervasive. Pseudocode for the lookup algorithm appears in Figure ©3.18.

The lower right portion of Figure (3.19 contains the skeleton of a Modula-2 program. The remainder of the figure shows the configuration of the symbol table for the referencing environment of the with statement in procedure P2. The scope stack contains four entries representing, respectively, the with statement, procedure P2, module M, and the global scope. The scope for the with statement indicates the specific record variable to which names (fields) in this scope belong. The outermost, pervasive scope is not explicitly represented.

All of the entries for a given name appear on the same hash chain, since the table is keyed on name. In this example, A2, F2, and T have also ended up on a single chain, due to hash collisions. Variables V and I (M's I) have extra entries, to make them visible across the boundary of closed scope M. When we are inside

#### example 3.45

Symbol table for a sample program

**Figure 3.19** LeBlanc-Cook symbol table for an example program in a language like Modula-2. The scope stack represents the referencing environment of the with statement in procedure P2. For the sake of clarity, the many pointers from type fields to the symbol table entries for integer and real are shown as parenthesized (1)s and (2)s, rather than as arrows.

Copyright © 2009 by Elsevier Inc. All rights reserved.

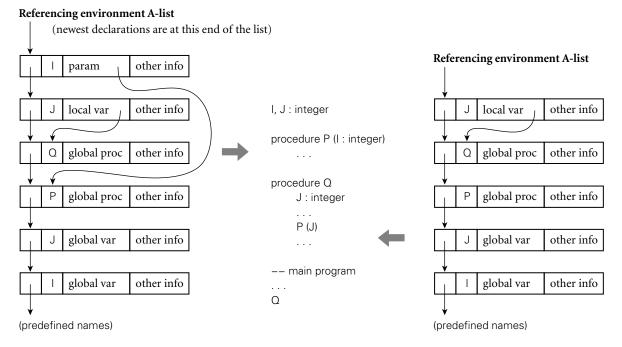

# **Figure 3.20** Dynamic scoping with an association list. The left side of the figure shows the referencing environment at the point in the code indicated by the adjacent grey arrow: after the main program calls $\Omega$ and it in turn calls P. When searching for I, one will find the parameter at the beginning of the A-list. The right side of the figure shows the environment at the other grey arrow: after P returns to $\Omega$ . When searching for I, one will find the global definition.

P2, a lookup operation on I will find P2's I; neither of the entries for M's I will be visible. The entry for type T indicates the scope number to be pushed onto the scope stack during with statements. The entry for each subroutine contains the head pointer of a list that links together the subroutine's parameters, for use in analyzing calls (additional links of these chains are not shown). During code generation, many symbol table entries would contain additional fields, for such information as size and run-time address.

## 3.4.2 Association Lists and Central Reference Tables

Pictorial representations of the two principal implementations of dynamic scoping appear in Figures (3.20 and (3.21). Association lists are simple and elegant, but can be very inefficient. Central reference tables resemble a simplified LeBlanc-Cook symbol table, without the separate scope stack; they require more work at scope entry and exit than do association lists, but they make *lookup* operations fast. A-lists are widely used for dictionary abstractions in Lisp; they are supported

by a rich set of built-in functions in most Lisp dialects. It is therefore natural

EXAMPLE 3.46 A-list lookup in Lisp

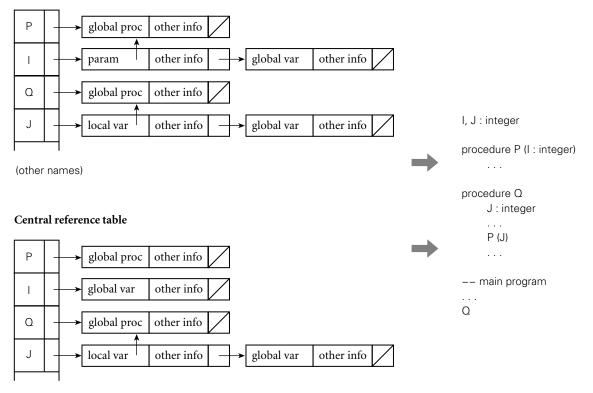

#### Central reference table

(each table entry points to the newest declaration of the given name)

(other names)

**Figure 3.21** Dynamic scoping with a central reference table. The upper half of the figure shows the referencing environment at the point in the code indicated by the upper grey arrow: after the main program calls Q and it in turn calls P. When searching for I, one will find the parameter at the beginning of the chain in the I slot of the table. The lower half of the figure shows the environment at the lower grey arrow: after P returns to Q. When searching for I, one will find the global definition.

for Lisp interpreters to use an A-list to keep track of name-value bindings, and even to make this list explicitly visible to the running program. Since bindings are created when entering a scope, and destroyed when leaving or returning from a scope, the A-list functions as a stack. When execution enters a scope at run time, the interpreter pushes bindings for names declared in that scope onto the top of the A-list. When execution finally leaves a scope, these bindings are removed. To look up the meaning of a name in an expression, the interpreter searches from the top of the list until it finds an appropriate binding (or reaches the end of the list, in which case an error has occurred). Each entry in the list contains whatever information is needed to perform semantic checks (e.g., type checking, which we will consider in Section 7.2) and to find variables and other objects that occupy memory locations. In the left half of Figure 03.20, the first (top) entry on the A-list represents the most recently encountered declaration: the | in procedure P. The second entry represents the J in procedure Q. Below these are the global symbols, Q, P, J, and I, and (not shown explicitly) any predefined names provided by the Lisp interpreter.

The problem with using an association list to represent a program's referencing environment is that it can take a long time to find a particular entry in the list, particularly if it represents an object declared in a scope encountered early in the program's execution, and now buried deep in the list. A central reference table is designed for faster access. It has one slot for every distinct name in the program. The table slot in turn contains a list (stack) of declarations encountered at run time, with the most recent occurrence at the beginning of the list. Looking up a name is now easy: the current meaning is found at the beginning of the list in the appropriate slot in the table. In the upper part of Figure (§ 3.21, the first entry on the | list is the | in procedure P; the second is the global |. If the program is compiled and the set of names is known at compile time, then each name can have a statically assigned slot in the table, which the compiled code can refer to directly. If the program is not compiled, or the set of names is not statically known, then a hash function will need to be used at run time to find the appropriate slot.

When control enters a new scope at run time, entries must be pushed onto the beginning of every list in the central reference table whose name is (re)declared in that scope. When control leaves a scope for the final time, these entries must be popped. The work involved is somewhat more expensive than pushing and popping an A-list, but not dramatically more so, and lookup operations are now much faster. In contrast to the symbol table of a compiler for a language with static scoping, central reference table entries for a given scope do not need to be saved when the scope completes execution; the space can be reclaimed.

Within the Lisp community, implementation of dynamic scoping via an association list is sometimes called *deep binding*, because the lookup operation may need to look arbitrarily deep in the list. Implementation via a central reference table is sometimes called *shallow binding*, because it finds the current association at the head of a given reference chain. Unfortunately, the terms "deep and shallow binding" are also more widely used for a completely different purpose, discussed in Section 3.6. To avoid potential confusion, some authors use "deep and shallow access" [Seb08] or "deep and shallow search" [Fin96] for the implementations of dynamic scoping.

#### **Closures with Dynamic Scoping**

(This subsection is best read after Section 3.6.1.)

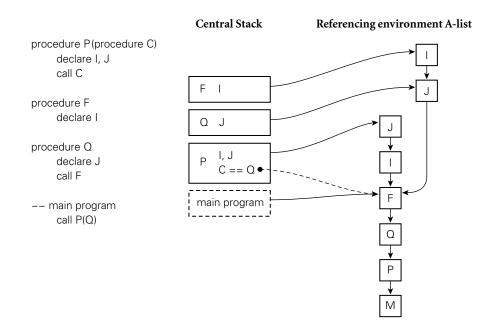

If an association list is used to represent the referencing environment of a program with dynamic scoping, the referencing environment in a closure can be represented by a top-of-stack (beginning of A-list) pointer (Figure ©3.22). When a subroutine is called through a closure, the main pointer to the referencing environment A-list is temporarily replaced by the pointer from the closure, making

#### EXAMPLE 3.47

Central reference table

EXAMPLE 3.48

A-list closures

**Figure 3.22** Capturing the A-list in a closure. Each frame in the stack has a pointer to the current beginning of the A-list, which the run-time system uses to look up names. When the main program passes Q to P with deep binding, it bundles its A-list pointer in Q's closure (dashed arrow). When P calls C (which is Q), it restores the bundled pointer. When Q elaborates its declaration of J (and F elaborates its declaration of I), the A-list is temporarily bifurcated.

any bindings created since the closure was created ( $P's \mid$  and J in the figure) temporarily invisible. New bindings created *within* the subroutine (or in any subroutine it calls) are pushed using the temporary pointer. Because the A-list is represented by pointers (rather than an array), the effect is to have two lists— one representing the caller's referencing environment and the other temporary referencing environment resulting from use of the closure—that share their older entries. When Q returns to P in our example, the original head of the A-list will be restored, making P's | and J visible again.

With a central reference table implementation of dynamic scoping, the creation of a closure is more complicated. In the general case, it may be necessary to copy the entire main array of the central table and the first entry on each of its lists. Space and time overhead may be reduced if the compiler or interpreter is able to determine that only some of the program's names will be used by the subroutine in the closure (or by things that the subroutine may call). In this case, the environment can be saved by copying the first entries of the lists for only the names that will be used. When the subroutine is called through the closure, these entries can then be pushed onto the beginnings of the appropriate lists in the central reference table. Additional code must be executed to remove them again after the subroutine returns.

## CHECK YOUR UNDERSTANDING

- 44. List the basic operations provided by a symbol table.

- 45. Outline the implementation of a LeBlanc-Cook style symbol table.

- **46.** Why don't compilers generally remove names from the symbol table at the ends of their scopes?

- **47.** Describe the *association list* (*A-list*) and *central reference table* data structures used to implement dynamic scoping. Summarize the tradeoffs between them.

- **48.** Explain how to implement deep binding by capturing the referencing environment A-list in a closure. Why are closures harder to build with a central reference table?

## Names, Scopes, and Bindings

## 3.8 Separate Compilation

Probably the most straightforward mechanisms for separate compilation can be found in module-based languages such as Modula-2, Modula-3, and Ada, which allow a module to be divided into a declaration part (or *header*) and an implementation part (or *body*). As we noted in Section 3.3.4, the header contains all and only the information needed by users of the module (or needed by the compiler in order to compile such a user); the body contains the rest.

As a matter of software engineering practice, a design team will typically define module interfaces early in the lifetime of a project, and codify these interfaces in the form of module headers. Individual team members or subteams will then work to implement the module bodies. While doing so, they can compile their code successfully using the headers for the other modules. Using preliminary copies of the bodies, they may also be able to undertake a certain amount of testing.

In a simple implementation, only the body of a module needs to be compiled into runnable code: the compiler can read the header of module M when compiling the body of M, and also when compiling the body of any module that uses M. In a more sophisticated implementation, the compiler can avoid the overhead of repeatedly scanning, parsing, and analyzing M's header by translating it into a symbol table, which is then accessed directly when compiling the bodies of M and its users. Most Ada implementations compile their module headers. Implementations of Modula-2 and 3 vary: some work one way, some the other.

As a practical matter, many languages allow the header of a module to be subdivided into a "public" part, which specifies the interface to the rest of the program, and a "private" part, which is not visible outside the module, but is needed by the compiler, for example to determine the storage requirements of opaque types. Ideally, one would include in the header of a module only that information that the programmer needs to know to use the abstraction(s) that the module provides. Restricted exports, and the public and private portions of headers, are compromises introduced to allow the compiler to generate code in the face of separate compilation. At some point prior to execution, modules that have been separately compiled must be "glued together" to form a single program. This job is the task of the *linker*. At the very least, the linker must resolve cross-module references (loads, stores, jumps) and *relocate* any instructions whose encoding depends on the location of certain modules in the final program. Typically it also checks to make sure that users and implementors of a given interface agree on the version of the header file used to define that interface. In some environments, the linker may perform additional tasks as well, including certain kinds of interprocedural (whole-program) code improvement. We will return to the subject of linking in Chapters 14 and 15.

## 3.8.1 Separate Compilation in C

The initial version of C was designed at Bell Laboratories around 1970. It has evolved considerably over the years, but not, for the most part, in the area of separate compilation. Here the language remains comparatively primitive. In particular, there is in general no way for the compiler or the linker to detect inconsistencies among declarations or uses of a name in different files. The C89 standards committee introduced a new explanation of separate compilation based on the notion of *linkage*, but this served mainly to clarify semantics, not to change them. The current rules can be summarized as follows (certain details and special cases are omitted):

- If the declaration of a global object (variable or function) contains the word static, then the object has *internal linkage*, and is identified with (linked to) any other internally linked declaration of the same name in the same file.

- If the declaration of a function does not contain the keyword static, then it has *external linkage*, and is identified with any other (nonstatic) declaration of the same function in any file of the program. (A function declaration may consist of just the header.)

- If the declaration of a variable contains the keyword extern, then the variable has the same linkage as any visible, internally or externally linked declaration of the same name appearing earlier in the file. If there is no earlier declaration, then the variable has external linkage, and is identified with any other declaration of the same external variable in any file of the program. In other words, files in the same program that contain matching external variable declarations actually share the same variable. A global variable also has external linkage if its declaration says neither static nor extern.

- If an object is declared with both internal and external linkage, the behavior of the program is undefined.

- An object (variable or function) that is externally linked must have a *definition* in exactly one file of a program. A variable is defined when it is given an initial value, or is declared at the global level without the extern keyword. A function is defined when its body (code) is given.

Many C implementations prior to C89 relaxed the final rule to permit zero or one definitions of an external variable; some permitted more than one. In these

implementations, the linker unified multiple definitions, and created an implicit definition for any variable (or set of linked variables) for which the program contained only declarations.